# **SOFTWARE DESCRIPTION**

**Enhanced Generic Test Software Library R&S®EGTSL**

# Software Description for ROHDE & SCHWARZ

## **Enhanced Generic Test Software Library R&S EGTSL**

6th Issue / 08.06 / D 1143.4140.42

This Software Description is valid for the R&S EGTSL-Software version **2.20** and the R&S GTSL-Software version **2.50** (and higher versions).

All rights, also translation into foreign languages, are reserved. No part of this manual is permitted to be reproduced in any form (print, photocopy or any other method), also not for the preparation of lectures, or processed, reproduced or made available using electronic systems without written permission from ROHDE & SCHWARZ.

® The passing on to third parties and the reproduction of this documentation, utilisation and communication of its contents is not permitted unless specifically approved. Infringements will incur claims for damages. All rights reserved in the case of the award of a patent or registration of a design.

$\ensuremath{\mathsf{R\&S}}^{\ensuremath{\mathbb{B}}}$  is a registered trademark of ROHDE & SCHWARZ GmbH & Co. KG.

We draw to your attention that the names of software and hardware used in the Software Description, and the brand names of the respective companies are, in general, the subject of protection as trademarks, or under proprietary rights, or patent law.

#### ROHDE & SCHWARZGmbH & Co. KG

Corporate Headquarters

Telephone:

...49 (0)89/4129-13774

Mühldorfstr. 15

Fax:

...49 (0)89/4129-13777

D-81671 München

...49 (0)89/4129-13777

Printed in the Federal Republic of Germany. Errors excepted, subject to technical change without notice.

# CERTIFICATE

## DQS GmbH

Deutsche Gesellschaft zur Zertifizierung von Managementsystemen

hereby certifies that the company

### Rohde & Schwarz GmbH & Co. KG

Mühldorfstrasse 15 D-81671 München

with the production sites as listed in the annex

for the scope Design and Development, Production, Sales, Services of Electronic-Measurement and Communication-Equipment and Systems

has implemented and maintains a

### Quality Management System.

An audit, documented in a report, has verified that this quality management system fulfills the requirements of the following standard:

**DIN EN ISO 9001: 2000**

December 2000 edition

The quality management system of the sites marked with (\*) in the annex fulfills the requirements set out by the international and German Road Traffic Regulations

including the approval objects as listed in the appendix.

This certificate is valid until

2008-01-23

Certificate Registration No.

001954 QM/ST

Frankfurt am Main

2005-01-24

This certificate is based on a quality audit in cooperation with the CETECOM ICT Services GmbH as a Notified Body under the Scope of the EC directive 99/5/EC. It was verified by the Notified Body that the supplementary requirements of the Annex V of the

European Concil Directive 99/5/EC are fulfilled.

Ass. iur. M. Drechsel

Luca

MANAGING DIRECTORS

cutive Officer of CETECOM ICT Services GmbH

Dipl.-Ing. J. Schirra

## Appendix to Certificate Registration No.: 001954 QM/ST

### Rohde & Schwarz GmbH & Co. KG

Mühldorfstrasse 15 D-81671 München

The international and German Road Traffic Law was audited regarding the following approval objects:

No.: 22 Electrical/Electronic Sub Assembly

## Annex to Certificate Registration No.: 001954 QM ST

#### Rohde & Schwarz GmbH & Co. KG

Mühldorfstrasse 15 D-81671 München

| Organ  | ization | al un | it/cita |

|--------|---------|-------|---------|

| Ulgail | IZALIUI | aı uı | IIVSILE |

#### ROHDE & SCHWARZ GmbH & Co. KG Service Centre Cologne ROHDE & SCHWARZ Systems GmbH Graf-Zeppelin-Strasse 18 D-51147 Köln

#### Rohde & Schwarz FTK GmbH Wendenschloßstrasse 168 D-12557 Berlin

#### Rohde & Schwarz GmbH & Co. KG Kaikenrieder Strasse 27 D-94244 Teisnach

### Rohde & Schwarz závod Vimperk s.r.o. Spidrova 49 CZE-38501 Vimperk Tschechische Republik

#### (\*) Rohde & Schwarz GmbH & Co. KG Mühldorfstrasse 15 81671 München

#### (\*) Rohde & Schwarz Messgerätebau GmbH Riedbachstrasse 58 D-87700 Memmingen

#### Scope

Technical services in the field of measuring/communication techniques maintenance/repair calibration training technical documentation

Development, production, systems

Design and Development, Production and Sale of Communication Equipment, Installations and systems

Design and Development, Production, Sales, Services of Electronic-Measurement and Communication-Equipment and Systems

Design and Development, Production, Sales, Services of Electronic-Measurement and Communication-Equipment and Systems

Design and Development, Production, Sales, Services of Electronic-Measurement and Communication-Equipment and Systems

Design and Development, Production, Sales, Services of Electronic-Measurement and Communication-Equipment and Systems

# **Support Center**

Telephone Europe: +49 180 512 42 42

Telephone worldwide: +49 89 4129 13774

Fax: +49 89 4129 13777

e-mail: customersupport@rohde-schwarz.com

If you have any technical queries about this Rohde & Schwarz equipment, our Hotline at the Support Center of Rohde & Schwarz Sales-GmbH will be glad to help.

Our team will discuss your queries and look for solutions to your problems.

The Hotline is open Mondays to Fridays from 08.00 to 17.00 hrs.

For queries outside office hours, you can leave a message or send a note via fax or email. We will then get back to you as soon as possible.

| 1 | Gen             | eral               |                                             | 1-1        |

|---|-----------------|--------------------|---------------------------------------------|------------|

|   | 1.1             | User in            | formation                                   | 1-1        |

|   | 1.2             | Referer            | nce documents                               | 1-1        |

|   | 1.3             | Explana            | ation of Symbols                            | 1-2        |

| 2 | Soft            | ware ins           | tallation                                   | 2-1        |

|   | 2.1             | Genera             | I                                           | 2-1        |

|   | 2.2             | Installa           | tion                                        | 2-1        |

|   | 2.3             | File stru          | ucture                                      | 2-7        |

| 3 | Fund            | ctional d          | escription                                  | 3-1        |

|   | 3.1             | Genera             | I                                           | 3-1        |

|   | 3.2             | ICT test           | t library                                   | 3-3        |

|   |                 | 3.2.1              | General                                     | 3-3        |

|   |                 | 3.2.2              | Entries in PHYSICAL.INI                     | 3-4        |

|   |                 | 3.2.3              | Entries in APPLICATION.INI                  | 3-5        |

|   |                 | 3.2.4              | Functions                                   | 3-6        |

|   | 3.3             | R&S E              | GTSL Loader                                 | 3-6        |

|   | 3.4             | R&S E              | 3-7                                         |            |

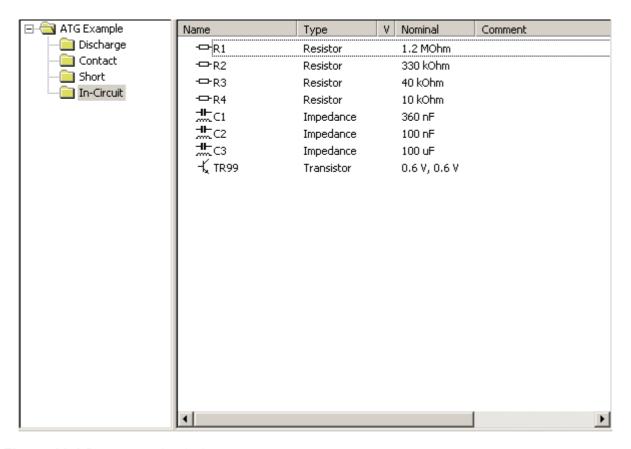

|   | 3.5             | Automa             | atic Test Generator ATG                     | 3-8        |

|   | 3.6             | ICT cor            | rection data                                | 3-8        |

|   | 3.7             | Hardwa             | re for in-circuit test                      | 3-9        |

| 4 | Getting Started |                    |                                             | 4-1        |

|   | 4.1             | Genera             | I                                           | 4-1        |

|   | 4.2             | Develo             | pment process for an in-circuit test        | 4-1        |

|   | 4.3             | Prepara            | ation of the circuit documentation          | 4-2        |

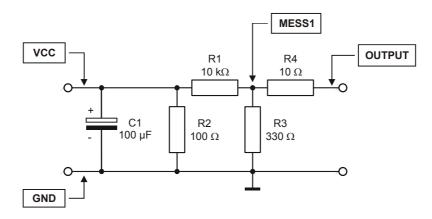

|   |                 | 4.3.1              | Example circuit                             | 4-2        |

|   |                 | 4.3.2              | Preparation of the circuit description      | 4-3        |

|   |                 | 4.3.2.1            | Entry of the resistors                      | 4-3        |

|   |                 | 4.3.2.2<br>4.3.2.3 | Entry of capacitors Entry of the transistor | 4-4<br>4-6 |

|   | 4.4             |                    | ng the ICT program                          | 4-7        |

|   | 4.5             | Adapte             | r manufacture                               | 4-8        |

|   |                 |                    |                                             | _          |

5

## Enhanced Generic Test Software Library R&S EGTSL

| 4.6      | Commi                                                        | ssioning and debugging                                                                            | 4-9                                                  |

|----------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Use      | r interfac                                                   | e (R&S EGTSL IDE)                                                                                 | 5-1                                                  |

| 5.1      | Genera                                                       | I                                                                                                 | 5-1                                                  |

| 5.2      | Menu s                                                       | tructure                                                                                          | 5-2                                                  |

| 5.3      | Main so                                                      | creen                                                                                             | 5-3                                                  |

| 5.4      | Sub-wii                                                      | ndow                                                                                              | 5-4                                                  |

| <b>O</b> | 5.4.1                                                        | Positioning of the sub-windows                                                                    | 5-4                                                  |

|          | <b>5.4.2</b> 5.4.2.1                                         | Program sub-window Context menu                                                                   | 5-5<br>5-6                                           |

|          | <b>5.4.3</b> 5.4.3.1                                         | Report sub-window<br>Context menu                                                                 | 5-7<br>5-8                                           |

|          | 5.4.4                                                        | Test Properties sub-window                                                                        | 5-8                                                  |

|          | <b>5.4.5</b> 5.4.5.1 5.4.5.2 5.4.5.3 5.4.5.4 5.4.5.5         | Results sub-window Context menu Results Tbl Results Gfx Results Hist Results Details              | 5-9<br>5-9<br>5-10<br>5-11<br>5-11                   |

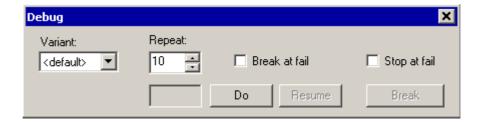

|          | 5.4.6                                                        | Debug sub-window                                                                                  | 5-12                                                 |

| 5.5      | Test St                                                      | eps                                                                                               | 5-15                                                 |

|          | <b>5.5.1</b> 5.5.1.1 5.5.1.2                                 | Contact General Results Details                                                                   | 5-15<br>5-15<br>5-16                                 |

|          | <b>5.5.2</b> 5.5.2.1 5.5.2.2 5.5.2.3                         | Continuity General Timing Results Details                                                         | 5-17<br>5-17<br>5-19<br>5-20                         |

|          | <b>5.5.3</b> 5.5.3.1 5.5.3.2 5.5.3.3 5.5.3.4 5.5.3.5         | Diode Limits Settings CNX Timing Results Details                                                  | 5-21<br>5-21<br>5-23<br>5-25<br>5-26<br>5-28         |

|          | <b>5.5.4</b> 5.5.4.1 5.5.4.2                                 | <b>Discharge</b><br>General<br>Results Details                                                    | 5-29<br>5-29<br>5-30                                 |

|          | <b>5.5.5</b> 5.5.5.1 5.5.5.2 5.5.5.3 5.5.5.4 5.5.5.5 5.5.5.6 | Impedance Limits Method Settings Timing Determination of measured value Results Details  Resistor | 5-31<br>5-31<br>5-32<br>5-35<br>5-37<br>5-38<br>5-40 |

|          | 5.5.6.1<br>5.5.6.2                                           | Limits Method                                                                                     | 5-41<br>5-42                                         |

## **Enhanced Generic Test Software Library R&S EGTSL**

Content

| 5.5.6.3<br>5.5.6.4<br>5.5.6.5                                 | Settings Timing Results Details                                                                                                                                                            | 5-45<br>5-47<br>5-49                         |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| <b>5.5.7</b> 5.5.7.1 5.5.7.2 5.5.7.3                          | Short General Timing Results Details                                                                                                                                                       | 5-50<br>5-50<br>5-52<br>5-53                 |

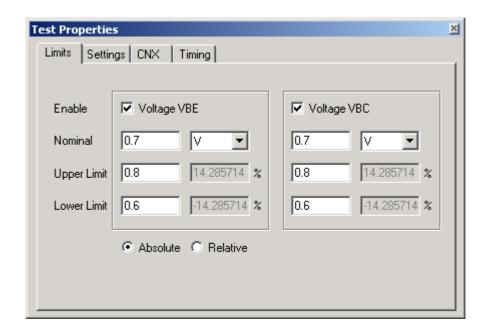

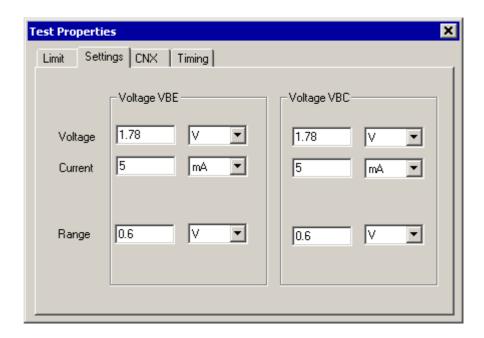

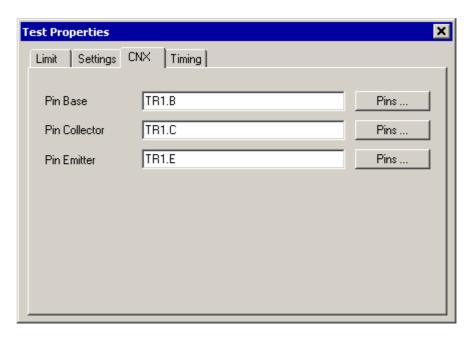

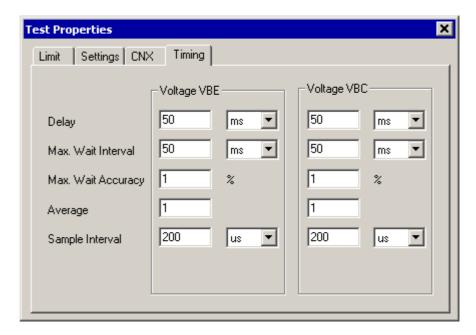

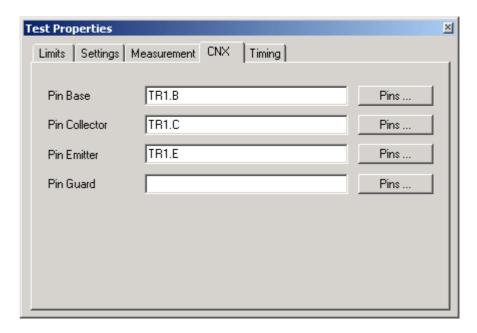

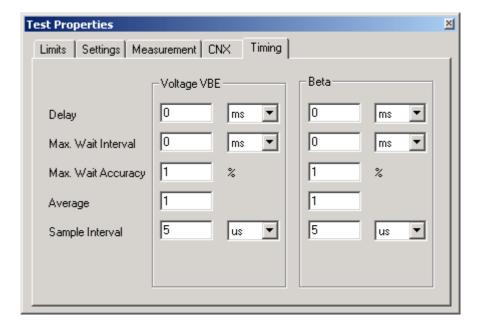

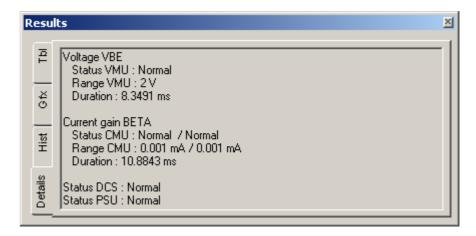

| <b>5.5.8</b> 5.5.8.1 5.5.8.2 5.5.8.3 5.5.8.4 5.5.8.5          | Transistor Limits Settings CNX Timing Results Details                                                                                                                                      | 5-54<br>5-54<br>5-55<br>5-56<br>5-57<br>5-59 |

| <b>5.5.9</b> 5.5.9.1 5.5.9.2 5.5.9.3 5.5.9.4 5.5.9.5 5.5.9.6  | Transistor Beta Limits Settings Measurement CNX Timing Results Details                                                                                                                     | 5-60<br>5-60<br>5-63<br>5-64<br>5-65<br>5-67 |

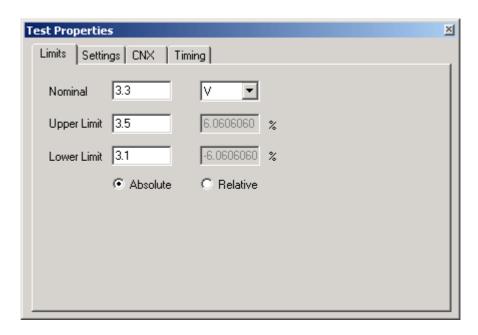

| <b>5.5.10</b> 5.5.10.1 5.5.10.2 5.5.10.3 5.5.10.4 5.5.10.5    | Zener Diode Limits Settings CNX Timing Results Details                                                                                                                                     | 5-69<br>5-69<br>5-70<br>5-71<br>5-72<br>5-74 |

| <b>5.5.11</b> 5.5.11.1 5.5.11.2                               | Explanations Timing Editing pin lists                                                                                                                                                      | 5-75<br>5-75<br>5-78                         |

| <b>5.5.12</b><br>5.5.12.1<br>5.5.12.2<br>5.5.12.3<br>5.5.12.4 | User-defined Test Methods Limits Settings Info Results Details                                                                                                                             | 5-80<br>5-80<br>5-81<br>5-82<br>5-83         |

| Menu bar                                                      | functions                                                                                                                                                                                  | 5-84                                         |

| <b>5.6.1</b> 5.6.1.2 5.6.1.3 5.6.1.4 5.6.1.5                  | Main menu command <file> Menu command <open> Menu command <save> Menu command <save as="" copy=""> Menu command <select> Menu command <close></close></select></save></save></open></file> | 5-84<br>5-85<br>5-85<br>5-86<br>5-86         |

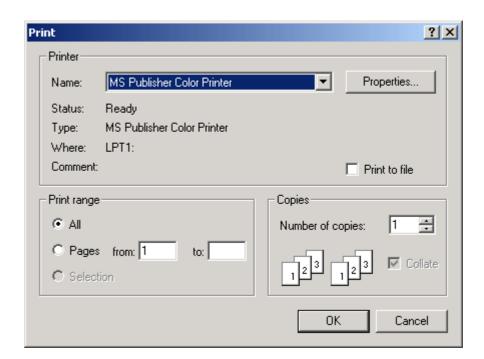

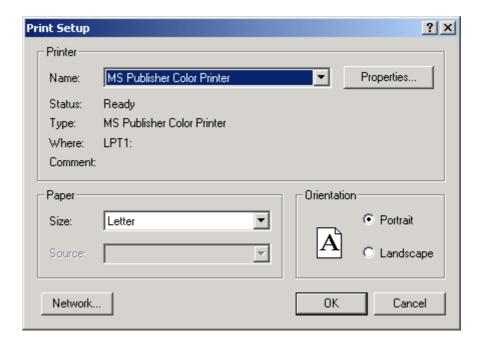

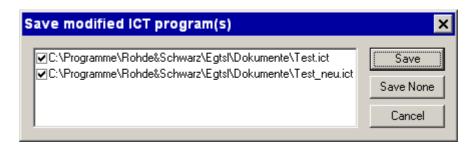

| 5.6.1.6<br>5.6.1.7<br>5.6.1.8<br>5.6.1.9<br>5.6.1.10          | Menu command <program properties=""> Menu command <limits> Menu command <print> Menu command <print setup=""> Menu command <exit></exit></print></print></limits></program>                | 5-87<br>5-90<br>5-93<br>5-94<br>5-95         |

| <b>5.6.2</b><br>5.6.2.2<br>5.6.2.3<br>5.6.2.4                 | Main menu command <edit> Functions Menu command <find> Menu command <step properties=""> Menu point <breakpoints></breakpoints></step></find></edit>                                       | 5-96<br>5-96<br>5-97<br>5-99<br>5-103        |

| 5.6.3                                                         | Main menu command <view></view>                                                                                                                                                            | 5-104                                        |

5.6

## Enhanced Generic Test Software Library R&S EGTSL

|   |                     | 5.6.4              | Main menu command <debug></debug>                           | 5-105      |  |

|---|---------------------|--------------------|-------------------------------------------------------------|------------|--|

|   |                     | 5.6.5              | Main menu command <report></report>                         | 5-107      |  |

|   |                     | 5.6.6              | Main menu command <help></help>                             | 5-108      |  |

|   |                     | 5.6.6.1            | Menu command <about egtsl=""></about>                       | 5-108      |  |

|   | 5.7                 | Toolbar            | functions                                                   | 5-109      |  |

|   |                     | 5.7.1              | Main Toolbar                                                | 5-109      |  |

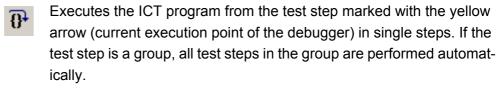

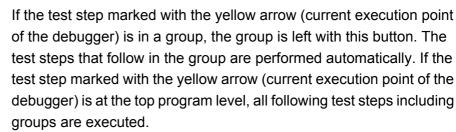

|   |                     | 5.7.2              | Debug Toolbar                                               | 5-110      |  |

|   |                     | 5.7.3              | Toolbar for Insert                                          | 5-112      |  |

|   |                     | 5.7.4              | Toolbar for user-defined tests                              | 5-113      |  |

|   | 5.8                 | Shortcut           | ts                                                          | 5-114      |  |

| 6 | Licen               | se mana            | gement                                                      | 6-1        |  |

| 7 | Confi               | iguration          | Files                                                       | 7-1        |  |

|   | 7.1                 | Syntax             |                                                             | 7-1        |  |

|   |                     | 7.1.1              | Naming conventions                                          | 7-1        |  |

|   |                     | 7.1.2              | [LogicalNames] section                                      | 7-2        |  |

|   |                     | 7.1.3              | [Device] section                                            | 7-3        |  |

|   |                     | 7.1.4              | [Bench] section                                             | 7-4        |  |

|   |                     | 7.1.5              | [ResourceManager] section                                   | 7-5        |  |

|   |                     | 7.1.6              | [Extlct] Section                                            | 7-5        |  |

|   | 7.2                 | PHYSICA            | AL.INI                                                      | 7-6        |  |

|   |                     | 7.2.1              | Example file for PHYSICAL.INI (Example_Physical.ini)        | 7-6        |  |

|   |                     | 7.2.2              | Description of example file PHYSICAL.INI                    | 7-7        |  |

|   | 7.3                 | APPLICA            | ATION.INI                                                   | 7-9        |  |

|   |                     | 7.3.1              | Example file for APPLICATION.INI (Example1_Application.ini) | 7-9        |  |

|   |                     | 7.3.2              | Description of example file APPLICATION.INI                 | 7-10       |  |

| 8 | Circuit description |                    |                                                             |            |  |

|   | 8.1                 | Definitio          | n of metalanguage                                           | 8-1        |  |

|   |                     | 8.1.1              | Terminology, symbols                                        | 8-1        |  |

|   |                     | 8.1.2              | Structure of a metaprogram                                  | 8-2        |  |

|   |                     | 8.1.3              | Structure of rule bodies                                    | 8-3        |  |

|   | 8.2                 | External           | file format (BDL)                                           | 8-6        |  |

|   |                     | 8.2.1              | Syntax                                                      | 8-6        |  |

|   |                     | 8.2.1.1<br>8.2.1.2 | Resistor List Variable Resistor List                        | 8-6<br>8-7 |  |

|   |                     | 8.2.1.3            | Potentiometer List                                          | 8-7<br>8-7 |  |

|   |                     | 8.2.1.4            | Resistor Array List                                         | 8-8        |  |

|   |                     | 8.2.1.5            | Capacitor List                                              | 8-8<br>8-9 |  |

|   |                     | 8.2.1.6<br>8.2.1.7 | Pol. Capacitor List Inductor List                           | 8-9<br>8-9 |  |

|   |                     | 8218               | Diode List                                                  | 8-10       |  |

## **Enhanced Generic Test Software Library R&S EGTSL**

LED List

8.2.1.9

9.3.2

**ATG** report

Content

8-10

|   |      | 8.2.1.10               | Zener Diode List                                                                   | 8-10         |

|---|------|------------------------|------------------------------------------------------------------------------------|--------------|

|   |      | 8.2.1.11               | Transistor List                                                                    | 8-11         |

|   |      | 8.2.1.12               | Jumper List                                                                        | 8-11         |

|   |      | 8.2.1.13<br>8.2.1.14   | IC List Connector List                                                             | 8-11<br>8-12 |

|   |      | 8.2.1.15               | Black Box List                                                                     | 8-12         |

|   |      | 8.2.1.16               | Track List                                                                         | 8-12         |

|   |      | 8.2.1.17               | Node List                                                                          | 8-13         |

|   |      | 8.2.1.18               | Basic constructs                                                                   | 8-13         |

|   |      | 8.2.2                  | Semantics                                                                          | 8-15         |

|   |      | 8.2.2.1                | General                                                                            | 8-15         |

|   |      | 8.2.2.2                | Resistor List                                                                      | 8-16         |

|   |      | 8.2.2.3<br>8.2.2.4     | Variable Resistor List Potentiometer List                                          | 8-17<br>8-18 |

|   |      | 8.2.2.5                | Resistor Array List                                                                | 8-19         |

|   |      | 8.2.2.6                | Capacitor List                                                                     | 8-21         |

|   |      | 8.2.2.7                | Pol. Capacitor List                                                                | 8-22         |

|   |      | 8.2.2.8                | Inductor List                                                                      | 8-23         |

|   |      | 8.2.2.9                | Diode List                                                                         | 8-25         |

|   |      | 8.2.2.10               | LED List                                                                           | 8-26         |

|   |      | 8.2.2.11               | Zener Diode List                                                                   | 8-27         |

|   |      | 8.2.2.12               | Transistor List                                                                    | 8-29         |

|   |      | 8.2.2.13<br>8.2.2.14   | Jumper List<br>IC List                                                             | 8-31<br>8-32 |

|   |      | 8.2.2.15               | Connector List                                                                     | 8-33         |

|   |      | 8.2.2.16               | Black Box List                                                                     | 8-34         |

|   |      | 8.2.2.17               | Track List                                                                         | 8-35         |

|   |      | 8.2.2.18               | Node List                                                                          | 8-36         |

|   | 8.3  | Importa                | nt additional Information                                                          | 8-37         |

|   |      | 8.3.1                  | Node List                                                                          | 8-37         |

|   |      | 8.3.2                  | Treatment of specific Pins                                                         | 8-37         |

| 9 | Auto | matic tes              | st generation with ATG                                                             | 9-1          |

|   | 9.1  | Function               | n                                                                                  | 9-1          |

|   | 9.2  | Starting               | ig the Automatic Test Generator ATG                                                |              |

|   | 9.3  | Output I               | Files                                                                              | 9-8          |

|   |      | 9.3.1                  | ICT program                                                                        | 9-8          |

|   |      | 9.3.1.1                | General                                                                            | 9-8          |

|   |      | 9.3.1.2                | Layout of the test program                                                         | 9-8          |

|   |      | 9.3.1.3                | State of the automatically generated test program                                  | 9-8          |

|   |      | 9.3.1.4                | Program groups generated                                                           | 9-9          |

|   |      | 9.3.1.4.1              | Capacitor discharging (Discharge)                                                  | 9-9          |

|   |      | 9.3.1.4.2<br>9.3.1.4.3 | Contact test (Contact) Continuity and short circuit test (Short)                   | 9-9<br>9-10  |

|   |      | 9.3.1.4.3              | Continuity and short-circuit test (Short)  The automatically generated analog test | 9-10<br>9-11 |

|   |      | 9.3.1.5                | Automatic determination of the guard points in the analog test                     | 9-12         |

|   |      | 9.3.1.6                | Safety against destruction of components during the test                           | 9-12         |

|   |      | 9317                   | Taking account of topological problems                                             | 9-13         |

9-13

## Enhanced Generic Test Software Library R&S EGTSL

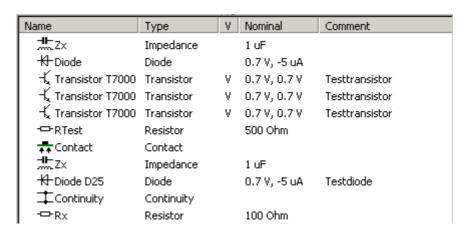

|    |        | 9.3.2.1<br>9.3.2.2<br>9.3.2.3 | Alternative proposals from the ATG  Test Coverage Report    | 9-14<br>9-15<br>9-17 |

|----|--------|-------------------------------|-------------------------------------------------------------|----------------------|

|    |        | 9.3.3                         | Application Layer Configuration File                        | 9-18                 |

|    |        | 9.3.4                         | Adapter manufacture                                         | 9-19                 |

| 10 | Test r | methods                       |                                                             | 10-1                 |

|    | 10.1   | Test hard                     | dware                                                       | 10-1                 |

|    | 10.2   | Ground v                      | wiring                                                      | 10-3                 |

|    | 10.3   | Contact                       | test                                                        | 10-4                 |

|    | 10.4   | Continui                      | ty test                                                     | 10-6                 |

|    | 10.5   | Diode tes                     | st                                                          | 10-7                 |

|    | 10.6   | Discharg                      | jing capacitors                                             | 10-9                 |

|    | 10.7   | Impedan                       | ce test                                                     | 10-11                |

|    |        | 10.7.1                        | 2- and 4-wire measurement                                   | 10-12                |

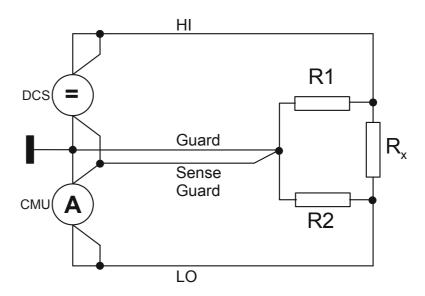

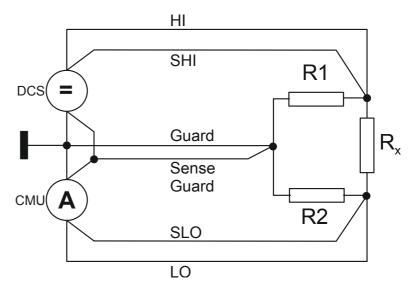

|    |        | 10.7.2                        | Guarded measurement                                         | 10-13                |

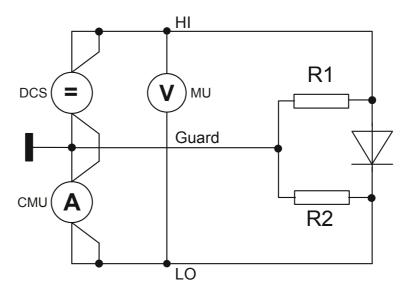

|    |        | 10.7.3                        | Correct phase impedance measurement                         | 10-16                |

|    |        | 10.7.4                        | System residuals                                            | 10-16                |

|    |        | 10.7.5                        | Measuring small capacitors                                  | 10-16                |

|    |        | 10.7.6                        | Measurement of polarized capacitors/electrolytic capacitors | 10-17                |

|    | 10.8   | Resistor                      | test                                                        | 10-18                |

|    |        | 10.8.1                        | 2-wire measurement                                          | 10-18                |

|    |        | 10.8.2                        | 4-wire measurement                                          | 10-20                |

|    |        | 10.8.3                        | Guarded measurement                                         | 10-21                |

|    | 10.9   | Short-cir                     | cuit test                                                   | 10-24                |

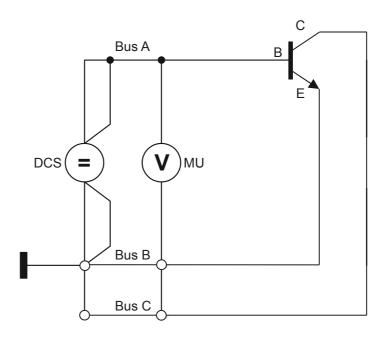

|    | 10.10  | Transisto                     | or test                                                     | 10-25                |

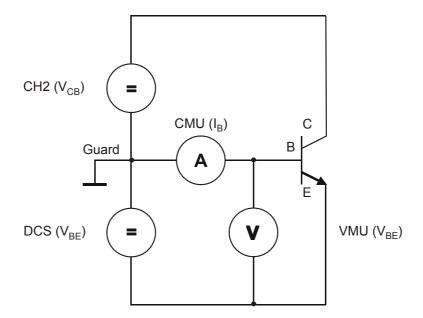

|    | 10.11  | Transisto                     | or Beta                                                     | 10-26                |

|    | 10.12  | Zener Diode                   |                                                             |                      |

| 11 | Creat  | ing test <sub>l</sub>         | programs                                                    | 11-1                 |

|    | 11.1   | Program                       | groups                                                      | 11-1                 |

|    | 11.2   | Variants                      |                                                             | 11-3                 |

|    |        | 11.2.1                        | Use                                                         | 11-3                 |

|    |        | 11.2.2                        | Definition                                                  | 11-4                 |

|    |        | 11.2.3                        | Assignment                                                  | 11-4                 |

|    |        | 11.2.4                        | Execution                                                   | 11-5                 |

|    | 11.3   | Limit File                    |                                                             | 11-6                 |

|    | 11.5   |                               | <del>, , , , , , , , , , , , , , , , , , , </del>           | 11-0                 |

| En | hanced | Generic 1 | Test Software Library R&S EGTSL                                      | Content |

|----|--------|-----------|----------------------------------------------------------------------|---------|

|    | 11.4   | Multiple  | panel testing                                                        | 11-7    |

|    |        | 11.4.1    | Example of an Application Layer Configuration File for Multiple Uses | 11-7    |

| 12 | Debu   | gger      | ·                                                                    | 12-1    |

|    | 12.1   | Overviev  | N                                                                    | 12-1    |

|    | 12.2   |           | and Terminating the Debugger                                         | 12-2    |

|    | 12.3   | Debug S   |                                                                      | 12-3    |

|    | 12.4   |           | e debugger                                                           | 12-4    |

|    | 12.5   | Breakpo   |                                                                      | 12-4    |

|    |        | •         |                                                                      |         |

|    | 12.6   | Stop cor  |                                                                      | 12-6    |

|    | 12.7   |           | debugging procedure                                                  | 12-7    |

|    | 12.8   | Measurii  | ng time optimization                                                 | 12-8    |

|    | 12.9   | Interpret | ation of the Results sub-window                                      | 12-9    |

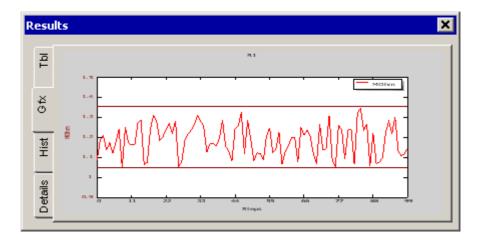

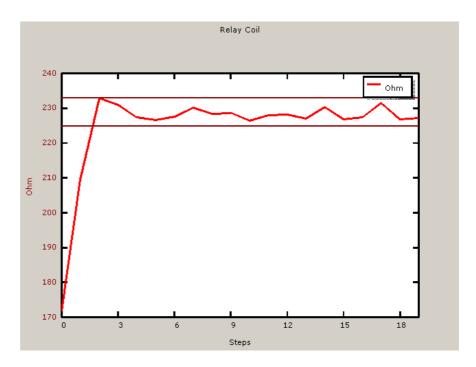

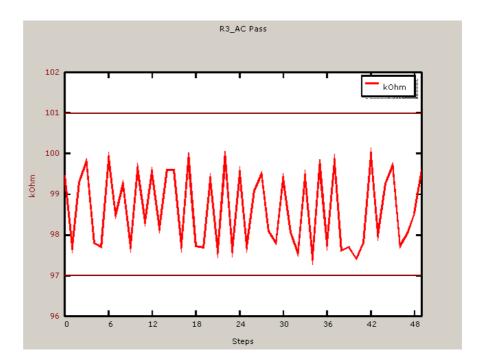

|    |        | 12.9.1    | Results Gfx sub-window                                               | 12-9    |

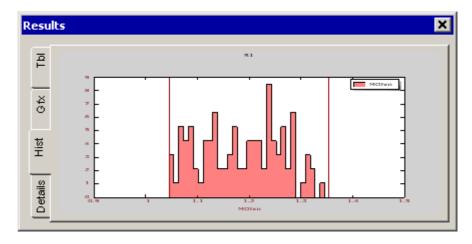

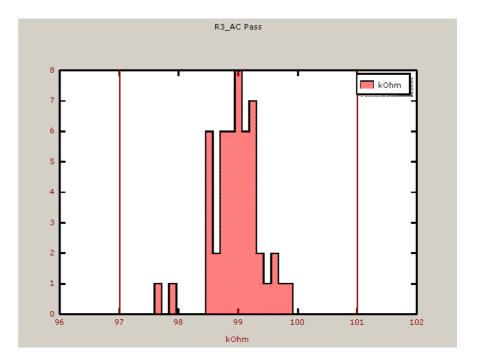

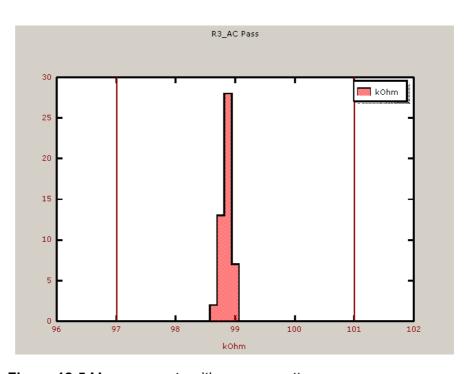

|    |        | 12.9.2    | Results Hist Sub-window                                              | 12-11   |

| 13 | Runn   | ing R&S   | EGTSL IDE                                                            | 13-1    |

|    | 13.1   | Starting  | using a function call from the ICT test library                      | 13-1    |

|    |        | 13.1.1    | Example                                                              | 13-2    |

|    | 13.2   | Starting  | using the R&S EGTSL Loader                                           | 13-5    |

|    |        | 13.2.1    | R&S EGTSL Loader, starting                                           | 13-6    |

| 14 | Repo   | rt Forma  | t                                                                    | 14-1    |

| 15 | ICT c  | orrection | n data                                                               | 15-1    |

| 16 | Error  | messag    | es                                                                   | 16-1    |

|    | 16.1   | Compile   | errors                                                               | 16-1    |

|    | 16.2   | Runtime   | Errors                                                               | 16-2    |

| 17 | ICT E  | xtension  | n Libraries                                                          | 17-1    |

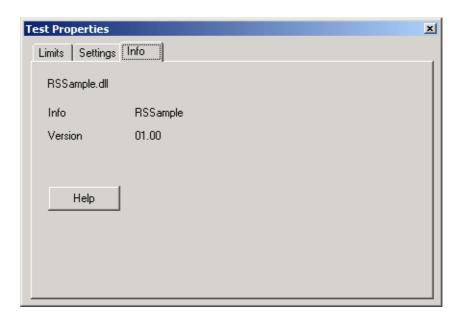

|    | 17.1   | Overviev  | N                                                                    | 17-1    |

|    |        | 17.1.1    | Objective                                                            | 17-1    |

|    |        | 17.1.2    | Functionality                                                        | 17-1    |

|    | 17.2   | Using Ex  | ktension Libraries                                                   | 17-2    |

|    |        | 17.2.1    | Configuration                                                        | 17-2    |

|    |        | 17.2.2    | Documentation                                                        | 17-2    |

|    |        | 17.2.3    | Inserting Test Steps                                                 | 17-3    |

## **Enhanced Generic Test Software Library R&S EGTSL**

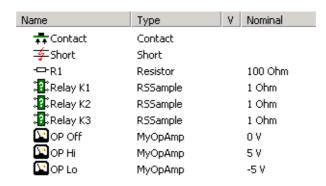

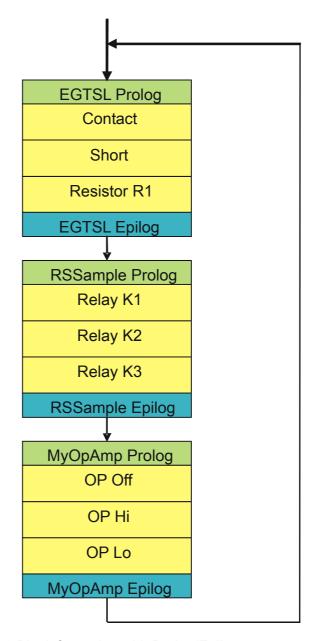

|      | 17.2.4                    | Grouping Test Steps                                         | 17-4           |

|------|---------------------------|-------------------------------------------------------------|----------------|

|      | 17.2.5                    | Running and Debugging Test Steps                            | 17-4           |

| 17.3 | Creating                  | Extension Libraries                                         | 17-5           |

|      | 17.3.1                    | Overview                                                    | 17-5           |

|      | 17.3.1.1                  | Software Structure                                          | 17-5           |

|      | 17.3.1.2                  | Working Principle                                           | 17-6           |

|      | 17.3.1.3                  | Integrating Hardware Modules                                | 17-6           |

|      | 17.3.1.4                  | File Structure                                              | 17-6           |

|      | 17.3.2                    | Sample Projects                                             | 17-7           |

|      | 17.3.2.1                  | RSSample                                                    | 17-7           |

|      | 17.3.2.2                  | Framework                                                   | 17-8           |

|      | 17.3.3                    | Internal Structure                                          | 17-8           |

|      | 17.3.3.1                  | Project Structure                                           | 17-8           |

|      | 17.3.3.2                  | Export interface                                            | 17-10          |

|      | 17.3.3.3                  | Data Structures                                             | 17-11          |

|      | 17.3.3.3.1                | Strings                                                     | 17-11          |

|      | 17.3.3.3.2                | Status                                                      | 17-12          |

|      | 17.3.3.3.3                | Test Result                                                 | 17-12          |

|      | 17.3.3.3.4                | Properties                                                  | 17-13          |

|      | 17.3.3.3.5                | Administrative Data                                         | 17-13          |

|      | 17.3.3.4                  | Support Functions                                           | 17-14          |

|      | 17.3.3.5                  | Bitmap                                                      | 17-15          |

|      | 17.3.4                    | Description of Function                                     | 17-16          |

|      | 17.3.4.1                  | Header Files                                                | 17-16          |

|      | 17.3.4.2                  | Exported Variables                                          | 17-16          |

|      | 17.3.4.2.1                | extictInfoTestName                                          | 17-17          |

|      | 17.3.4.2.2                | extictInfoVersion                                           | 17-17          |

|      | 17.3.4.2.3                | extictInfoHelpFileName                                      | 17-17          |

|      | 17.3.4.2.4                | extictInfoIconBitMap                                        | 17-18          |

|      | 17.3.4.3                  | Local Data Structures                                       | 17-18          |

|      | 17.3.4.3.1                | SetupUserData                                               | 17-18          |

|      | 17.3.4.3.2                |                                                             | 17-19          |

|      | 17.3.4.3.3                | Table of Properties                                         | 17-20          |

|      | 17.3.4.3.4                | Tables for Value Conversions                                | 17-22          |

|      | 17.3.4.4                  | Configuration functions                                     | 17-23          |

|      | 17.3.4.4.1                | extictConfigSetup                                           | 17-23          |

|      | 17.3.4.4.2                | extictConfigCleanup                                         | 17-23          |

|      | 17.3.4.4.3                | extictConfigProlog                                          | 17-24          |

|      | 17.3.4.4.4                | extictConfigEpilog                                          | 17-24          |

|      | 17.3.4.4.5                | extictConfigErrorCleanup                                    | 17-25          |

|      | 17.3.4.5                  | Test-related functions<br>extictTestConstruct               | 17-25          |

|      | 17.3.4.5.1                | extictTestDestruct                                          | 17-25<br>17-26 |

|      | 17.3.4.5.2<br>17.3.4.5.3  | extictTestCompile                                           | 17-26<br>17-26 |

|      | 17.3.4.5.3                | extictTestMeasure                                           | 17-26          |

|      | 17.3.4.5.4                | extictTestMeasure<br>extictTestGetDebugDetails              | 17-20          |

|      | 17.3.4.5.6                | extictTestGetDebugDetails<br>extictTestGetResultDescription | 17-27          |

|      | 17.3.4.6                  | Functions for displaying results                            | 17-28          |

|      | 17.3.4.6.1                | extictResultTableGetValueCaption                            | 17-28          |

|      | 17.3.4.6.2                | extictResultTableFormatValueString                          | 17-28          |

|      | 17.3.4.6.3                | extictResultTableFormatUnitString                           | 17-29          |

|      |                           | _                                                           |                |

|      | <b>17.3.5</b><br>17.3.5.1 | Details of implementation Error handling                    | 17-29<br>17-29 |

|      | 11.0.0.1                  | Enormaning                                                  | 11-23          |

## Enhanced Generic Test Software Library R&S EGTSL

Content

|   |             | 17.3.5.2             | Simulation                                            | 17-31      |

|---|-------------|----------------------|-------------------------------------------------------|------------|

|   |             | 17.3.5.3             | Tracing                                               | 17-32      |

|   |             | 17.3.5.4             | Locking                                               | 17-33      |

|   |             | 17.3.6               | R&S EGTSL-internal Hardware Modules                   | 17-34      |

|   |             | 17.3.7               | Additional Hardware Modules                           | 17-34      |

|   |             | 17.3.7.1             | Configuration of Hardware Modules                     | 17-35      |

|   |             | 17.3.7.2             | Co-operative Session Concept                          | 17-36      |

|   |             | 17.3.7.3             | Setup                                                 | 17-37      |

|   |             | 17.3.7.4             | Cleanup                                               | 17-37      |

|   |             | 17.3.7.5             | Prolog and Epilog                                     | 17-38      |

|   |             | 17.3.8               | Advanced Topics                                       | 17-40      |

|   |             | 17.3.8.1             | Debugging ICT Extension Libraries                     | 17-40      |

|   |             | 17.3.8.2             | Non-numeric Test Results                              | 17-40      |

|   |             | 17.3.8.3             | Time Optimisation                                     | 17-41      |

|   |             | 17.3.8.4<br>17.3.8.5 | Aspects of Compatibility                              | 17-42      |

|   |             | 17.3.8.5             | Communication between ICT Extension Libraries         | 17-43      |

| Α | Exan        | nple 1               |                                                       | A-1        |

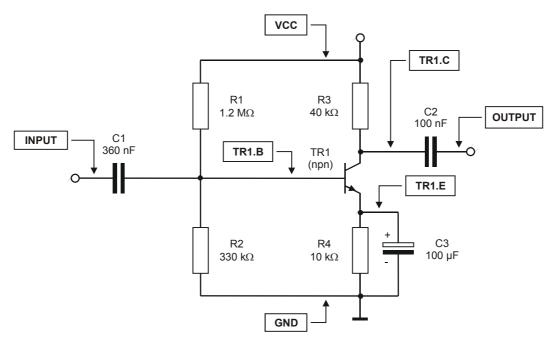

|   | <b>A</b> .1 | Circuit f            | for example 1                                         | <b>A-1</b> |

|   | A.2         | BDL file             | for example 1                                         | <b>A-1</b> |

|   | <b>A.3</b>  | ICT repo             | ort generated for example 1                           | A-3        |

|   | <b>A.4</b>  | Applicat             | tion Layer Configuration File generated for example 1 | <b>A-4</b> |

| В | Exan        | nple 2               |                                                       | B-1        |

|   | 5.4         |                      |                                                       | 5.         |

|   | B.1         | Circuit              | for example 2                                         | B-1        |

|   | B.2         | BDL file             | for example 2                                         | B-1        |

|   | B.3         | ICT repo             | ort generated for example 2                           | B-3        |

|   | B.4         | Applicat             | tion Laver Configuration File generated for example 2 | B-4        |

# **Figures**

| Figure 2-1  | Setup Welcome Screen                          | 2-2  |

|-------------|-----------------------------------------------|------|

| Figure 2-2  | Setup License Agreement                       | 2-2  |

| Figure 2-3  | Setup User Information                        | 2-3  |

| Figure 2-4  | Setup Choose Destination Location             | 2-3  |

| Figure 2-5  | Setup Select Program Components               | 2-4  |

| Figure 2-6  | Setup Settings                                | 2-4  |

| Figure 2-7  | Setup Status                                  | 2-5  |

| Figure 2-8  | Setup Complete                                | 2-5  |

| Figure 2-9  | File structure                                | 2-7  |

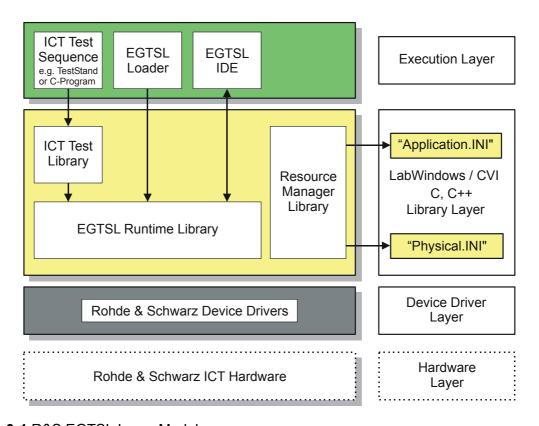

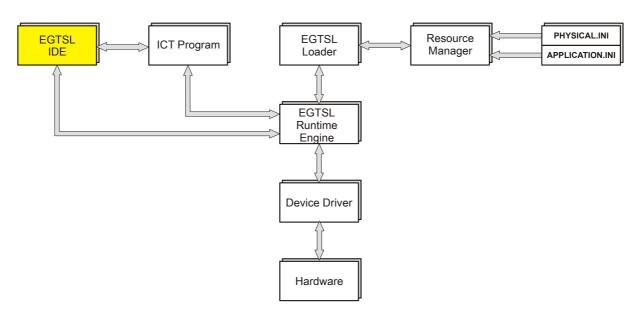

| Figure 3-1  | R&S EGTSL Layer Model                         | 3-1  |

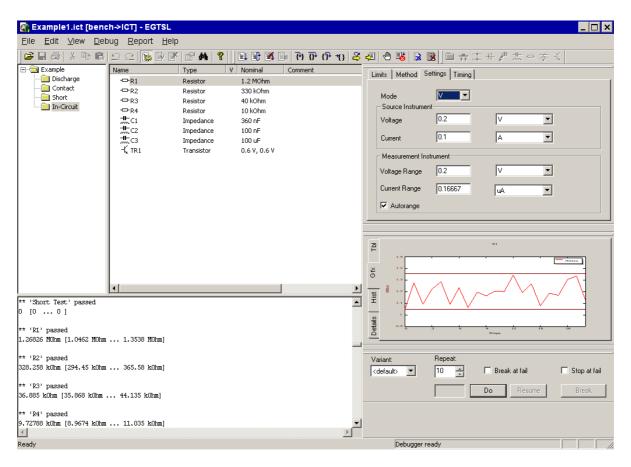

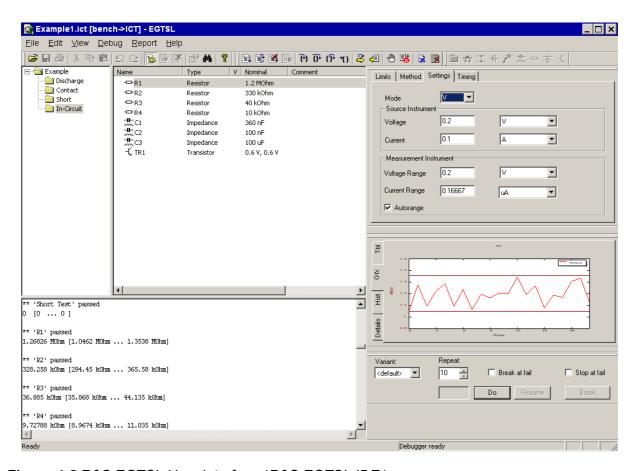

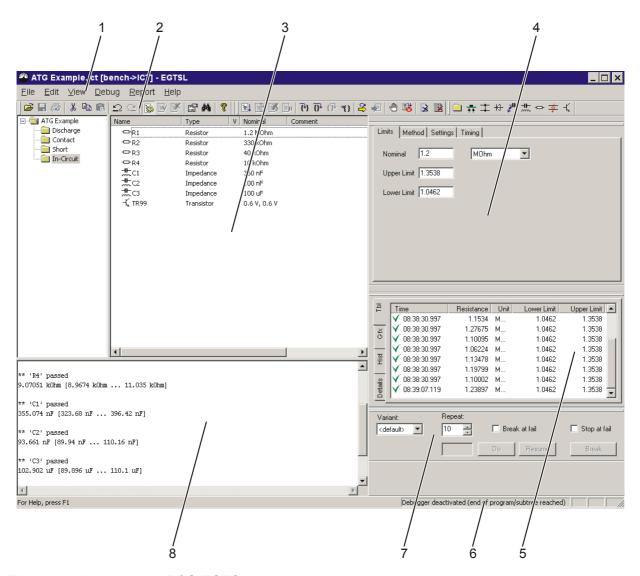

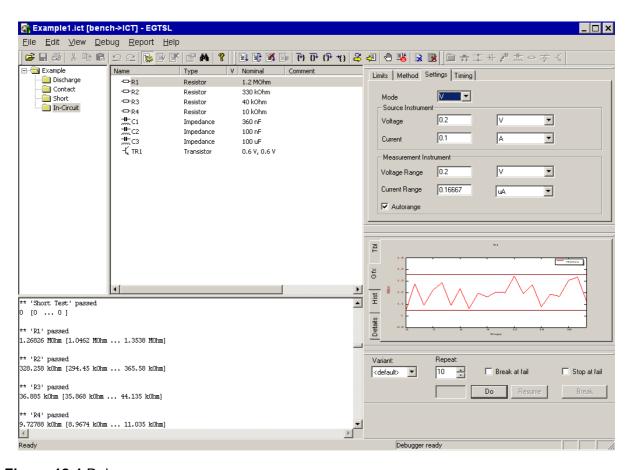

| Figure 3-2  | R&S EGTSL User interface (R&S EGTSL IDE)      | 3-7  |

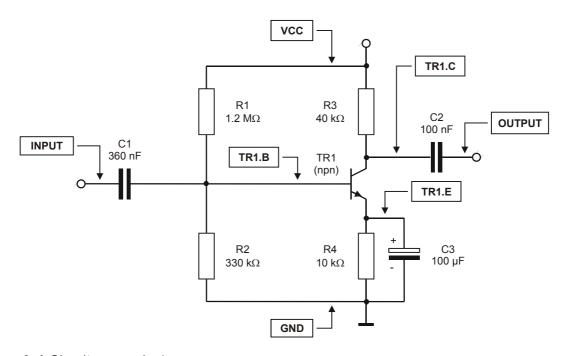

| Figure 4-1  | Circuit example 1                             | 4-2  |

| Figure 4-2  | R&S EGTSL User interface (R&S EGTSL IDE)      | 4-9  |

| Figure 5-1  | Menu structure                                | 5-2  |

| Figure 5-2  | Main screen R&S EGTSL                         | 5-3  |

| Figure 5-3  | Program sub-window                            | 5-5  |

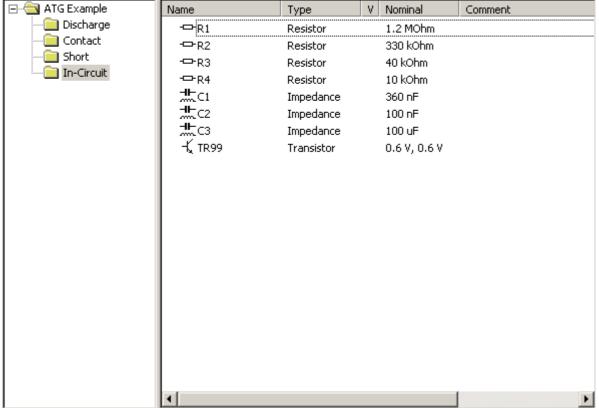

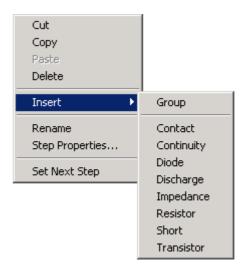

| Figure 5-4  | Program context menu                          | 5-6  |

| Figure 5-5  | Report sub-window                             | 5-7  |

| Figure 5-6  | Report context menu                           | 5-8  |

| Figure 5-7  | Results context menu                          | 5-9  |

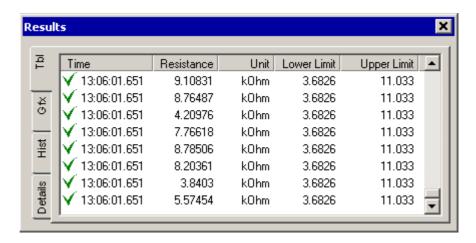

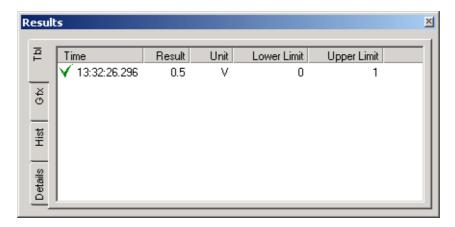

| Figure 5-8  | Results Table                                 | 5-9  |

| Figure 5-9  | Results Graphic                               | 5-10 |

| Figure 5-10 | Results History                               | 5-11 |

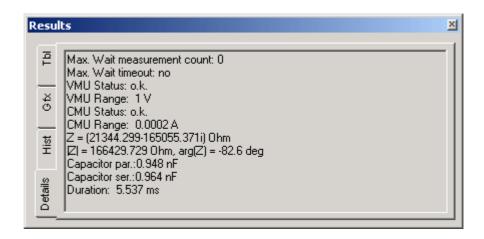

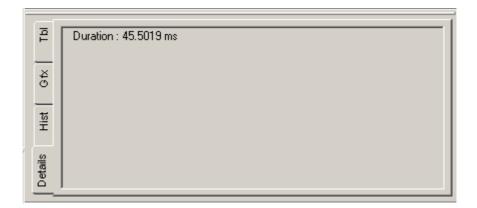

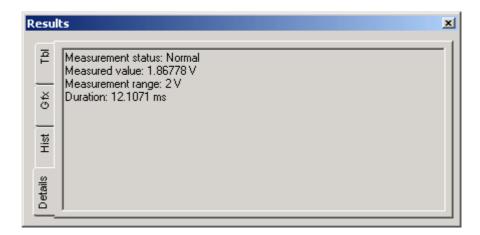

| Figure 5-11 | Results Details                               | 5-11 |

| Figure 5-12 | Results context menu                          | 5-12 |

| Figure 5-13 | Debug                                         | 5-12 |

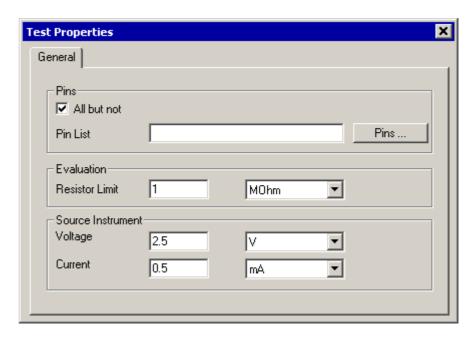

| Figure 5-14 | Test Step Contact, Test Properties General    | 5-15 |

| Figure 5-15 | Test Step Contact, Results Details            | 5-16 |

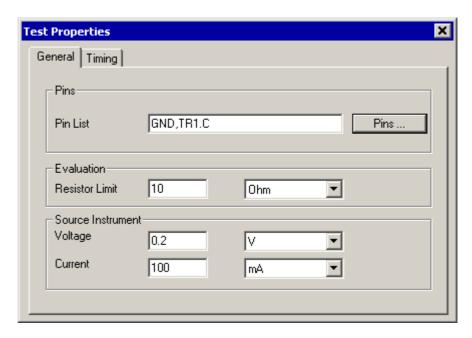

| Figure 5-16 | Test Step Continuity, Test Properties General | 5-17 |

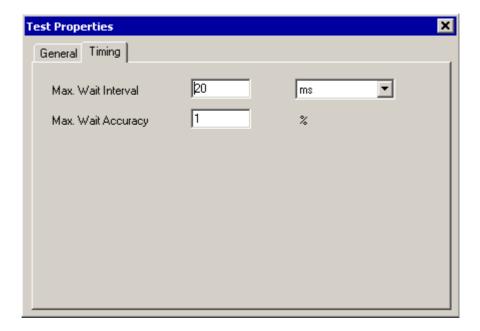

| Figure 5-17 | Test Step Continuity, Test Properties Timing  | 5-19 |

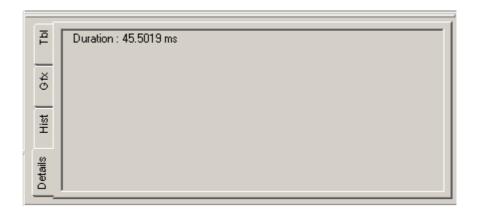

| Figure 5-18 | Test Step Continuity, Results Details         | 5-20 |

|             |                                               |      |

## Figures

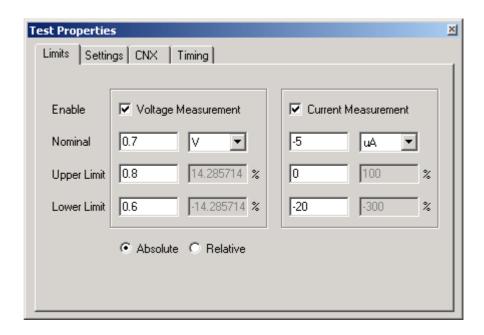

| Figure 5-19 | Test Step Diode, Test Properties Limits                         | 5-21 |

|-------------|-----------------------------------------------------------------|------|

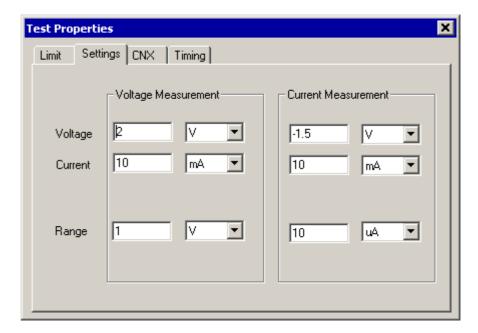

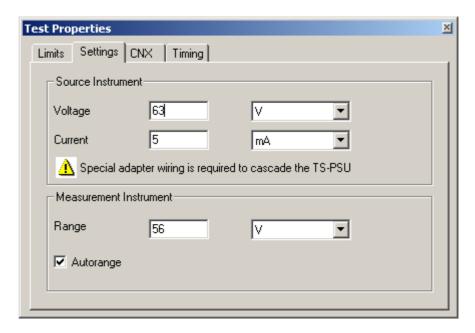

| Figure 5-20 | Test Step Diode, Test Properties Settings                       | 5-23 |

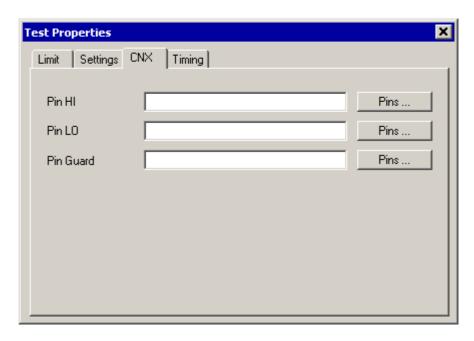

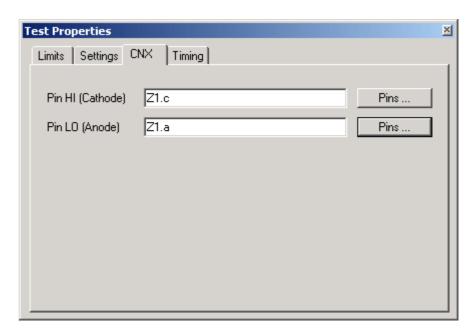

| Figure 5-21 | Test Step Diode, Test Properties CNX                            | 5-25 |

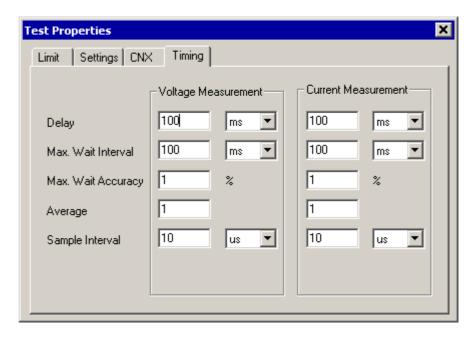

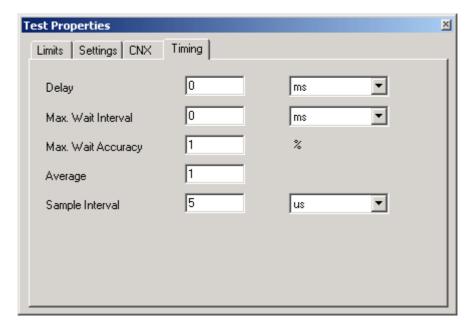

| Figure 5-22 | Test Step Diode, Test Properties Timing                         | 5-26 |

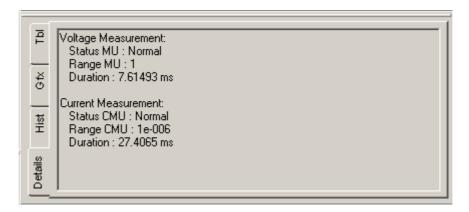

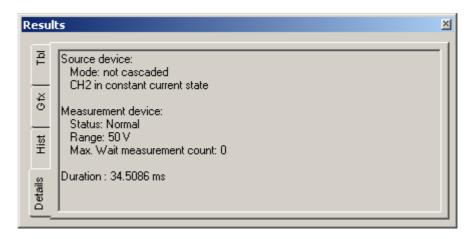

| Figure 5-23 | Test Step Diode, Results Details                                | 5-28 |

| Figure 5-24 | Test Step Discharge, Test Properties General                    | 5-29 |

| Figure 5-25 | Test Step Discharge, Results Details                            | 5-30 |

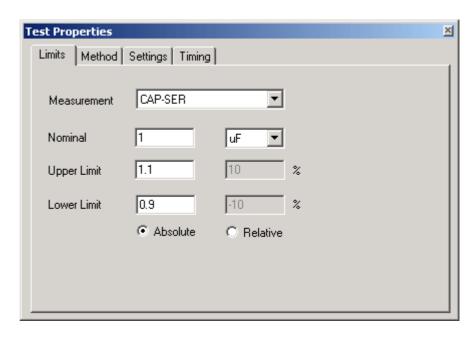

| Figure 5-26 | Test Step Impedance, Test Properties Limits                     | 5-31 |

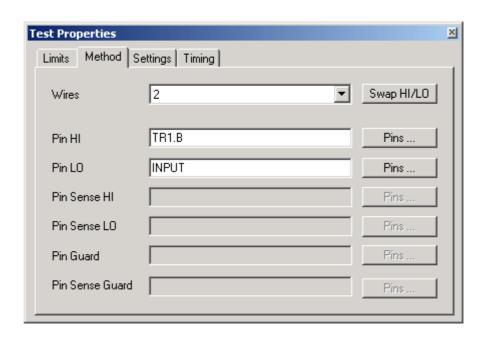

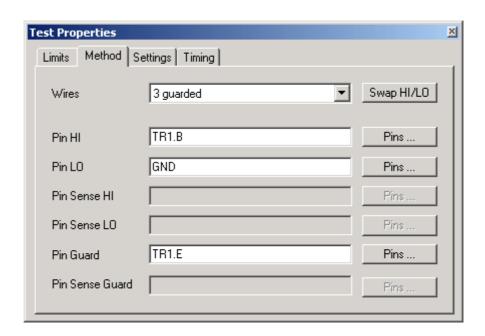

| Figure 5-27 | Test Step Impedance, Test Properties Method                     | 5-32 |

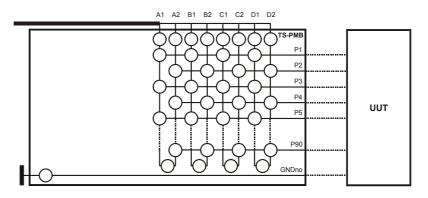

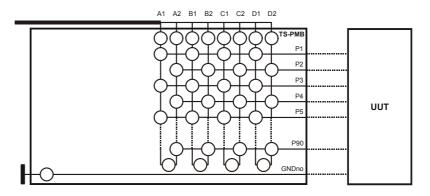

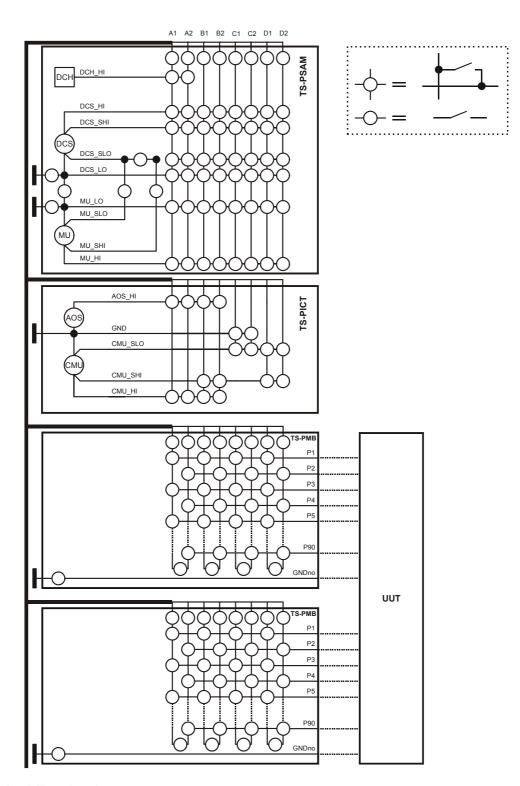

| Figure 5-28 | R&S TS-PMB wiring                                               | 5-33 |

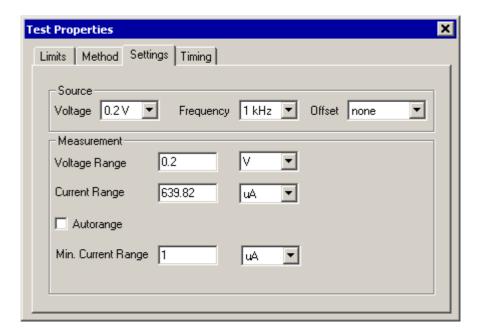

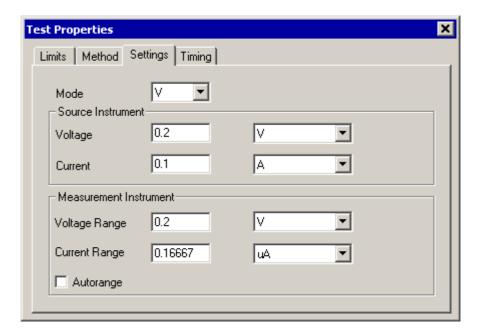

| Figure 5-29 | Test Step Impedance, Test Properties Settings                   | 5-35 |

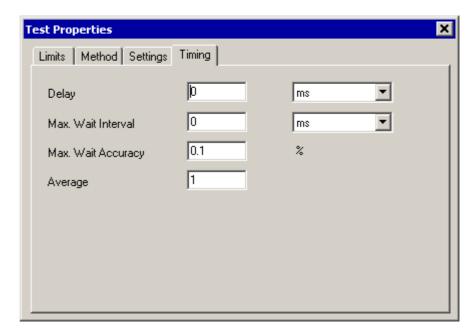

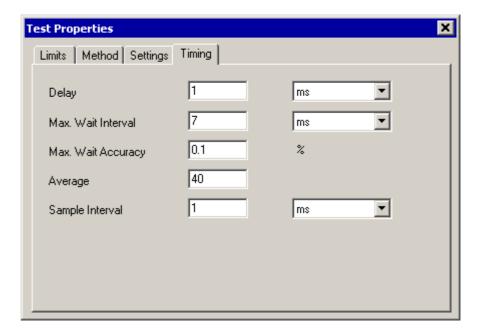

| Figure 5-30 | Test Step Impedance, Test Properties Timing                     | 5-37 |

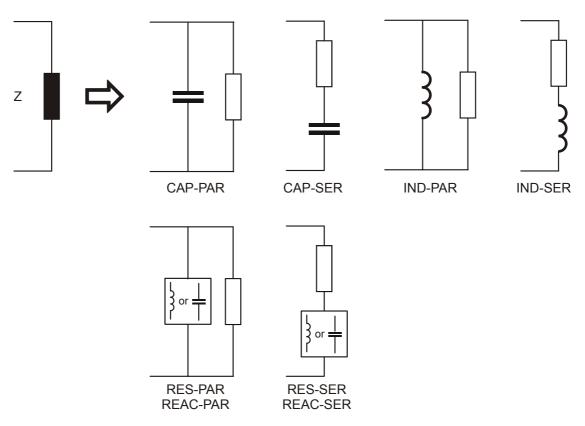

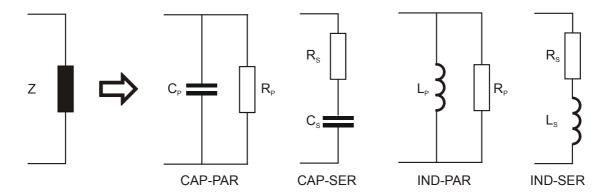

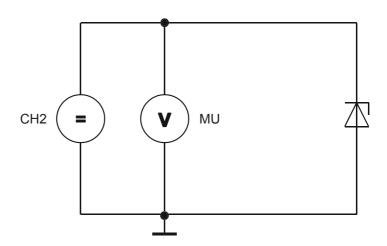

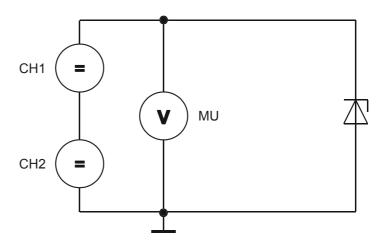

| Figure 5-31 | Equivalent circuit diagrams for determination of measured value | 5-38 |

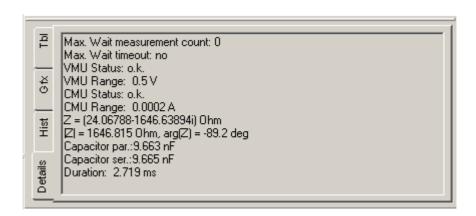

| Figure 5-32 | Test Step Impedance, Results Details                            | 5-40 |

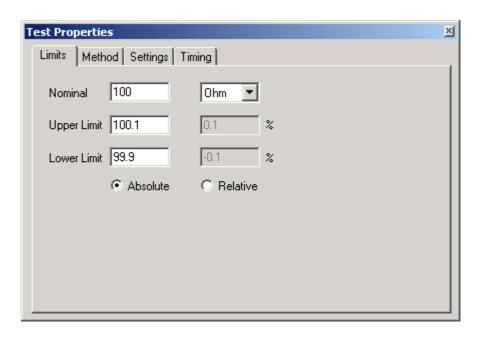

| Figure 5-33 | Test Step Resistor, Test Properties Limits                      | 5-41 |

| Figure 5-34 | Test Step Resistor, Test Properties Method                      | 5-42 |

| Figure 5-35 | TS-PMB wiring                                                   | 5-43 |

| Figure 5-36 | Test Step Resistor, Test Properties Settings                    | 5-45 |

| Figure 5-37 | Test Step Resistor, Test Properties Timing                      | 5-47 |

| Figure 5-38 | Test Step Resistor, Results Details                             | 5-49 |

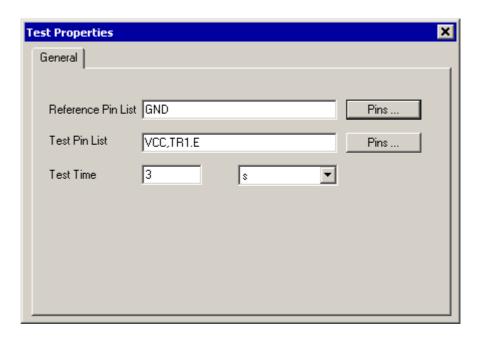

| Figure 5-39 | Test Step Short, Test Properties General                        | 5-50 |

| Figure 5-40 | Test Step Short, Test Properties Timing                         | 5-52 |

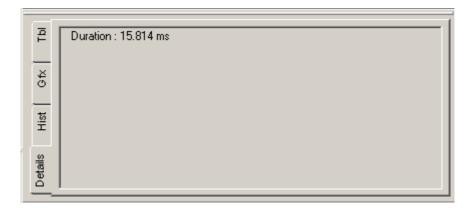

| Figure 5-41 | Test Step Short, Results Details                                | 5-53 |

| Figure 5-42 | Test Step Transistor, Test Properties Limits                    | 5-54 |

| Figure 5-43 | Test Step Transistor, Test Properties Settings                  | 5-55 |

| Figure 5-44 | Test Step Transistor, Test Properties CNX                       | 5-56 |

| Figure 5-45 | Test Step Transistor, Test Properties Timing                    | 5-57 |

| Figure 5-46 | Test Step Transistor, Results Details                           | 5-59 |

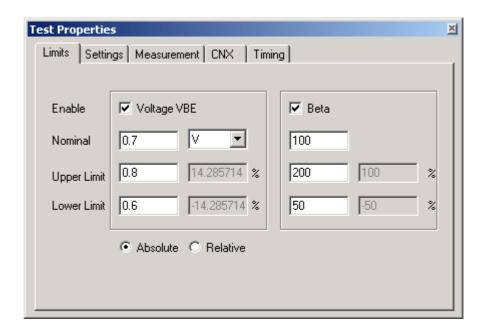

| Figure 5-47 | Test Step Transistor Beta, Test Properties Limits               | 5-60 |

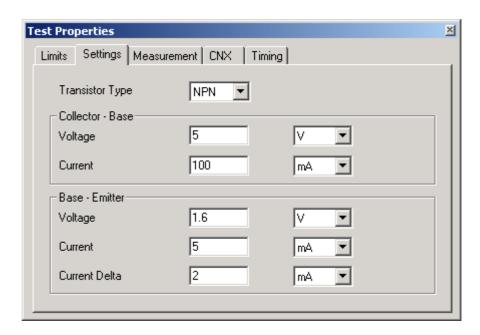

| Figure 5-48 | Test Step Transistor Beta, Test Properties Settings             | 5-61 |

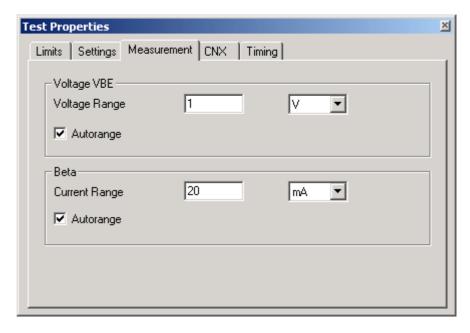

| Figure 5-49 | Test Step Transistor Beta, Test Properties Measurement          | 5-63 |

| Figure 5-50 | Test Step Transistor Beta, Test Properties CNX                  | 5-64 |

| Figure 5-51 | Test Step Transistor Beta, Test Properties Timing               | 5-65 |

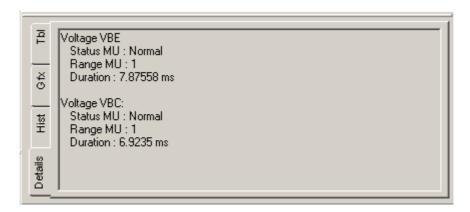

| Figure 5-52 | Test Step Transistor Beta, Results Details       | 5-67  |

|-------------|--------------------------------------------------|-------|

| Figure 5-53 | Test Step Zener Diode, Test Properties Limits    | 5-69  |

| Figure 5-54 | Test Step Zener Diode, Test Properties Settings  | 5-70  |

| Figure 5-55 | Test Step Zener Diode, Test Properties CNX       | 5-71  |

| Figure 5-56 | Test Step Zener Diode, Test Properties Timing    | 5-72  |

| Figure 5-57 | Test Step Zener Diode, Results Details           | 5-74  |

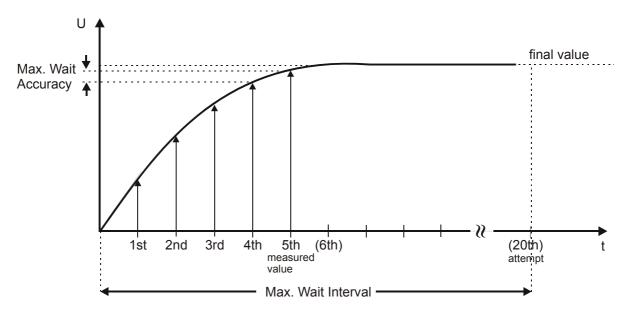

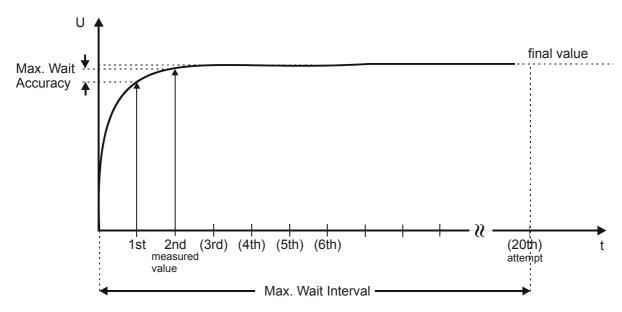

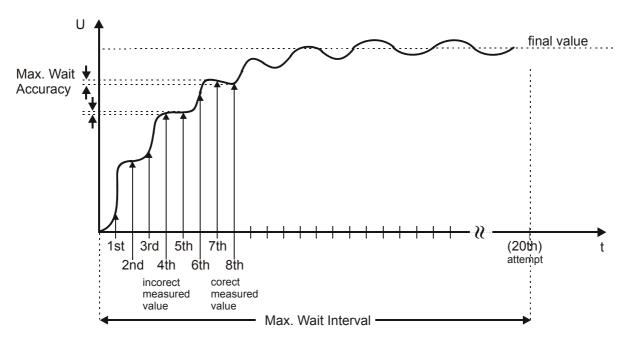

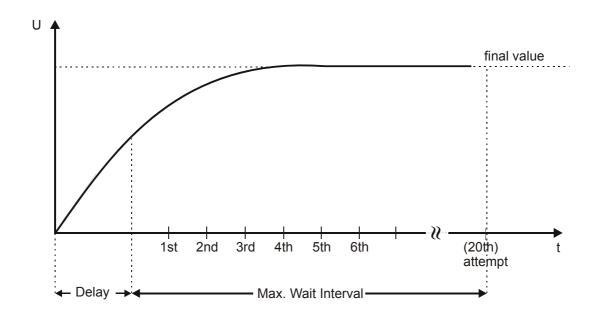

| Figure 5-58 | Timing example 1                                 | 5-75  |

| Figure 5-59 | Timing example 2                                 | 5-75  |

| Figure 5-60 | Timing example 3                                 | 5-76  |

| Figure 5-61 | Timing example 4                                 | 5-77  |

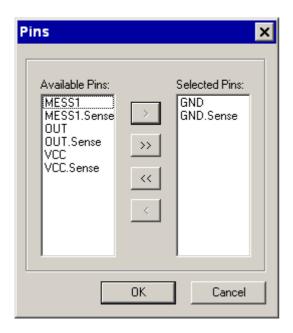

| Figure 5-62 | Pins dialog box                                  | 5-78  |

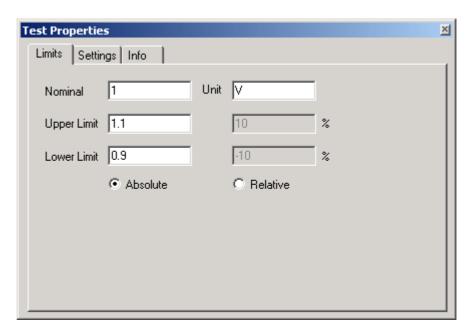

| Figure 5-63 | Test Step user-defined, Test Properties Limits   | 5-80  |

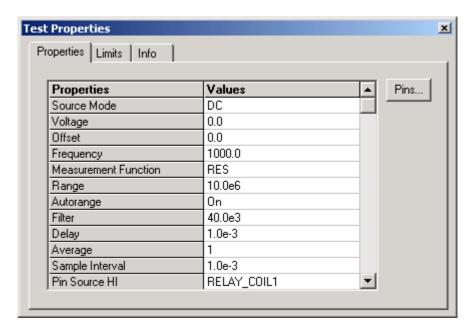

| Figure 5-64 | Test Step user-defined, Test Properties Settings | 5-81  |

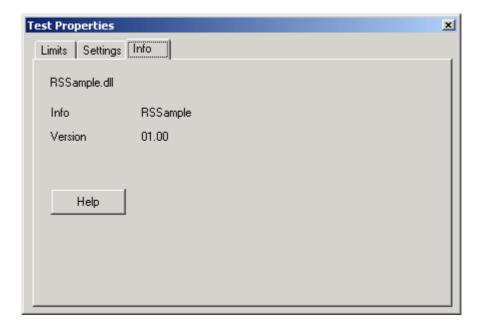

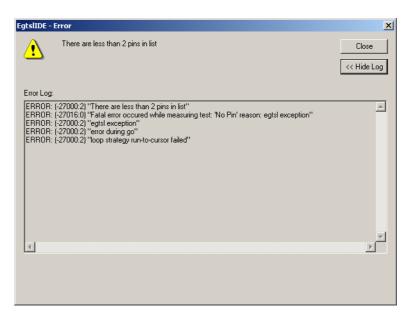

| Figure 5-65 | Test Step user-defined, Test Properties Info     | 5-82  |

| Figure 5-66 | Test Step user-defined, Results Details          | 5-83  |

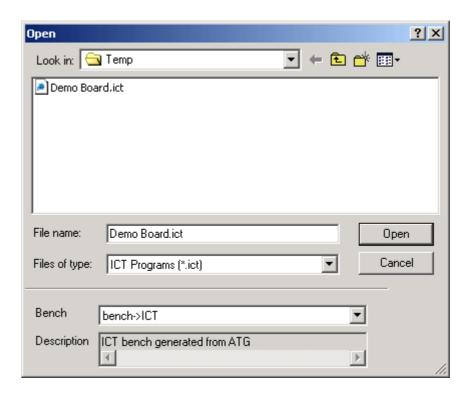

| Figure 5-67 | Open                                             | 5-84  |

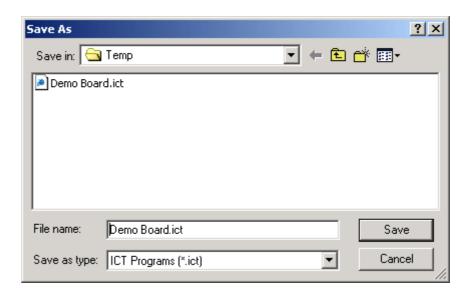

| Figure 5-68 | Save Copy As                                     | 5-85  |

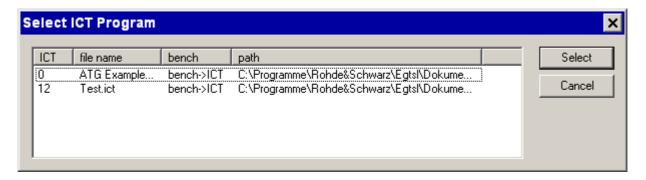

| Figure 5-69 | Select ICT Program                               | 5-86  |

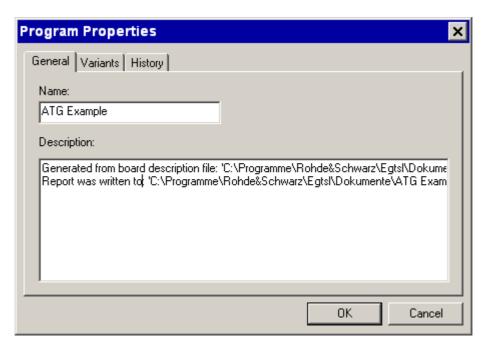

| Figure 5-70 | ICT Program Properties, General                  | 5-87  |

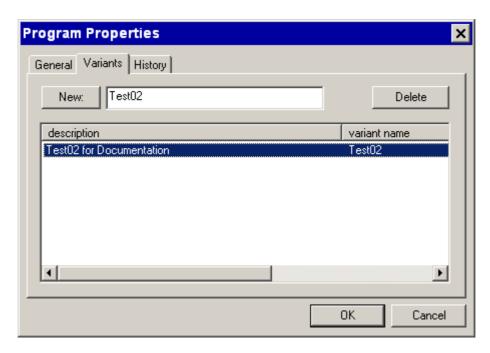

| Figure 5-71 | ICT Program Properties, Variants                 | 5-88  |

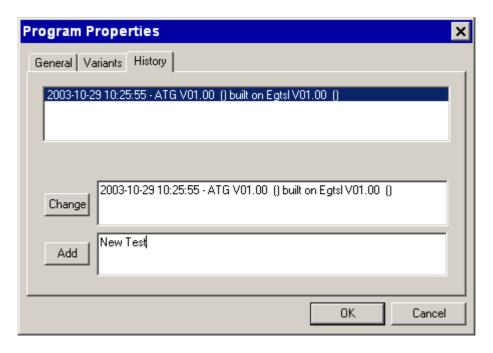

| Figure 5-72 | ICT Program Properties, History                  | 5-89  |

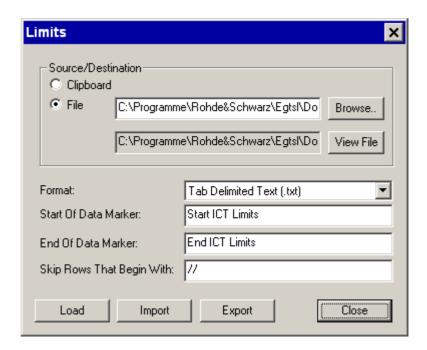

| Figure 5-73 | Limits                                           | 5-90  |

| Figure 5-74 | Print                                            | 5-93  |

| Figure 5-75 | Print Setup                                      | 5-94  |

| Figure 5-76 | Exit Warning                                     | 5-95  |

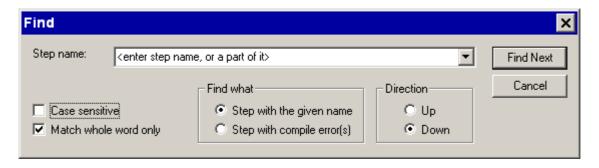

| Figure 5-77 | Find (Program)                                   | 5-97  |

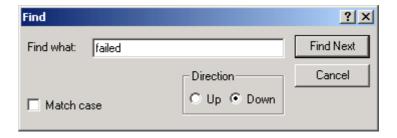

| Figure 5-78 | Find (Report)                                    | 5-98  |

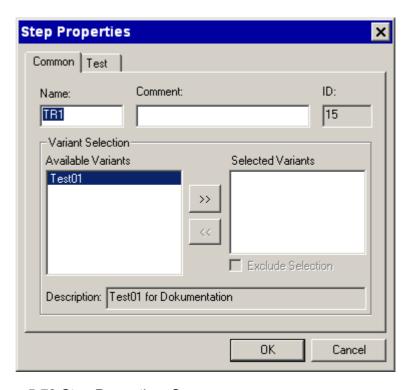

| Figure 5-79 | Step Properties, Common                          | 5-99  |

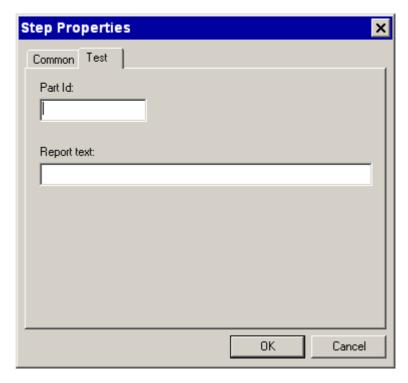

| Figure 5-80 | Step Properties, Test                            | 5-101 |

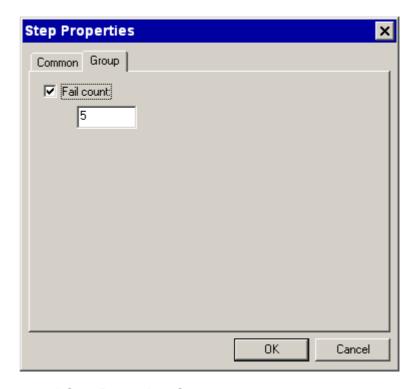

| Figure 5-81 | Step Properties, Group                           |       |

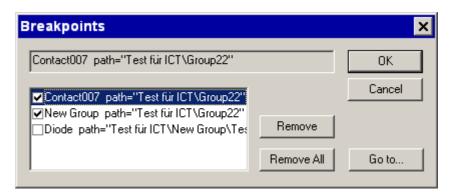

| Figure 5-82 | Breakpoints                                      | 5-103 |

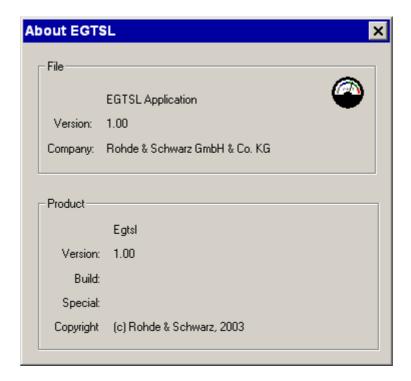

| Figure 5-83 | About EGTSL                                      |       |

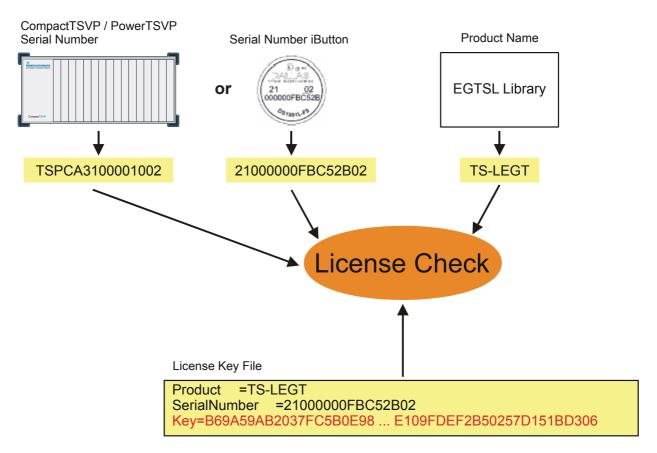

| Figure 6-1  | License checking                                 |       |

| Figure 8-1   | Priorities of the operators                                            | 8-5   |

|--------------|------------------------------------------------------------------------|-------|

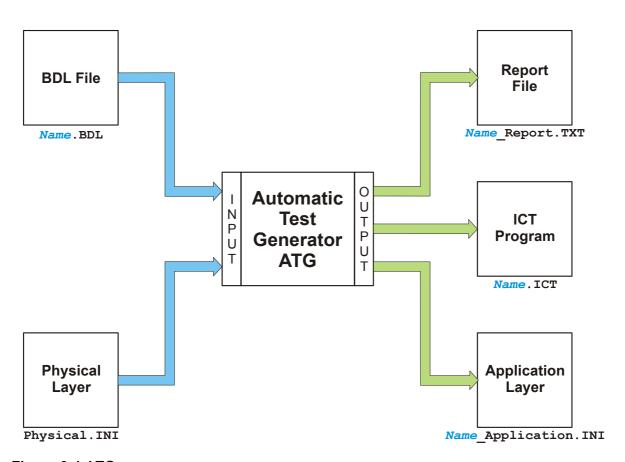

| Figure 9-1   | ATG sequence                                                           | 9-1   |

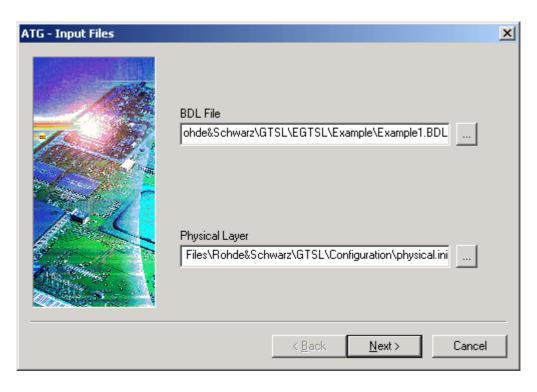

| Figure 9-2   | ATG - input files                                                      | 9-3   |

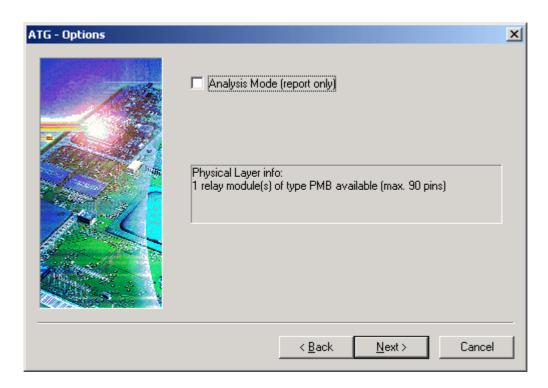

| Figure 9-3   | ATG - Options                                                          | 9-4   |

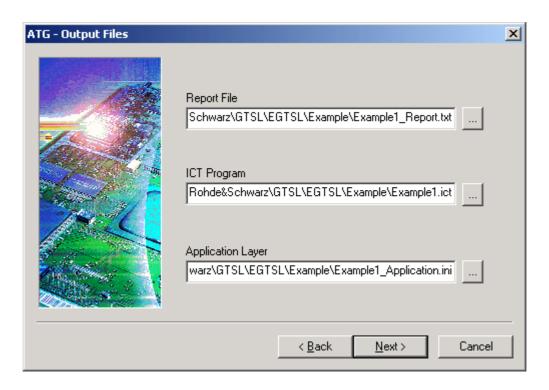

| Figure 9-4   | ATG - Output Files                                                     | 9-5   |

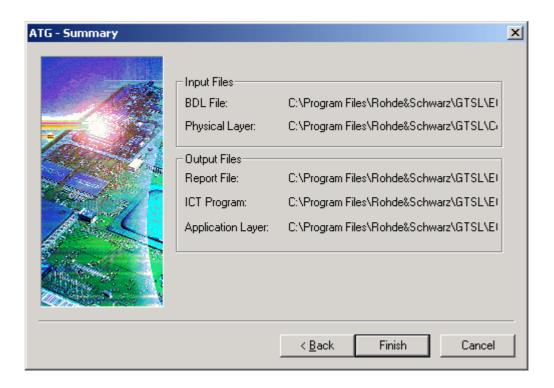

| Figure 9-5   | ATG - Summary                                                          | 9-6   |

| Figure 9-6   | ATG Process                                                            | 9-6   |

| Figure 9-7   | ATG Finish                                                             | 9-7   |

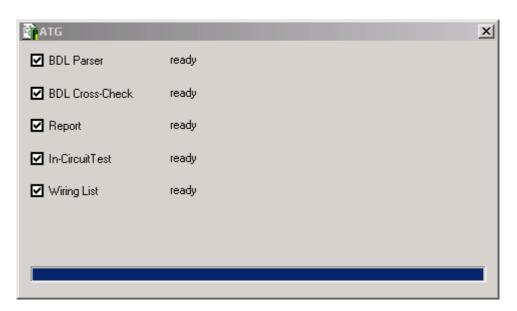

| Figure 10-1  | Test hardware                                                          | 10-1  |

| Figure 10-2  | Connection for contact test                                            | 10-4  |

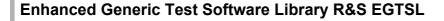

| Figure 10-3  | Diode test (forward bias voltage + reverse bias current)               | 10-7  |

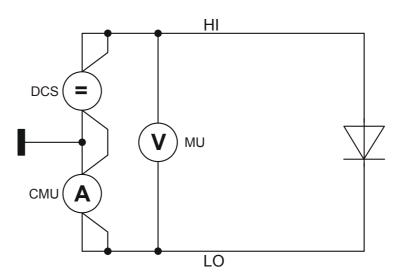

| Figure 10-4  | Diode test with guarding (forward bias voltage + reverse bias current) | 10-7  |

| Figure 10-5  | Discharge test                                                         |       |

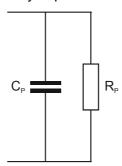

| Figure 10-6  | Equivalent circuit diagrams for determination of measured value        | 10-11 |

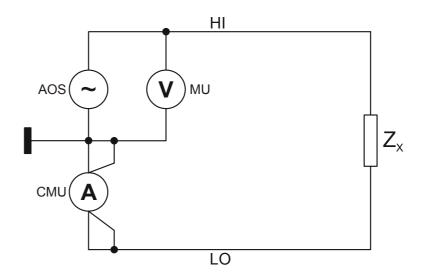

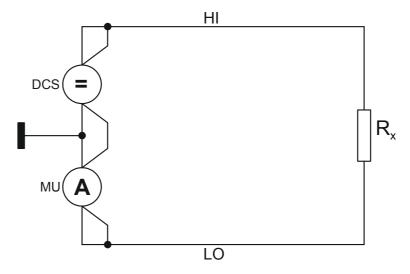

| Figure 10-7  | 2-wire impedance measurement (mode V)                                  | 10-12 |

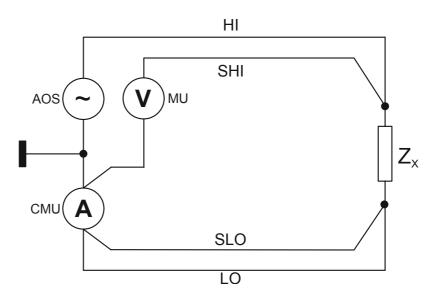

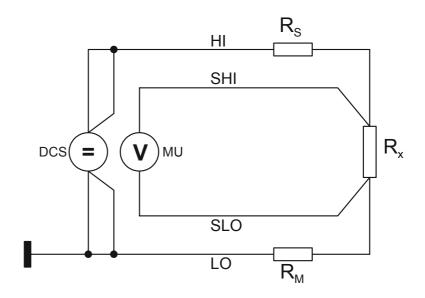

| Figure 10-8  | 4-wire impedance measurement (mode VS)                                 | 10-12 |

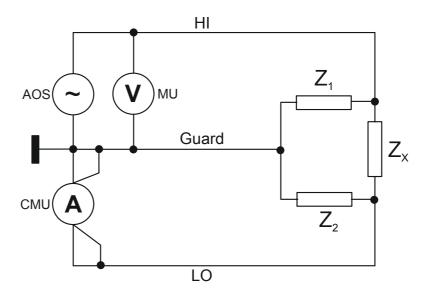

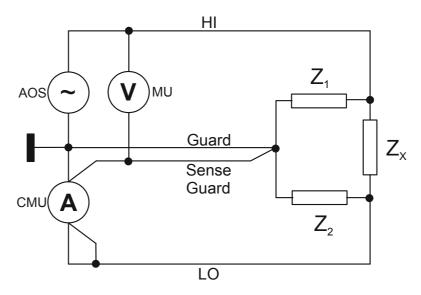

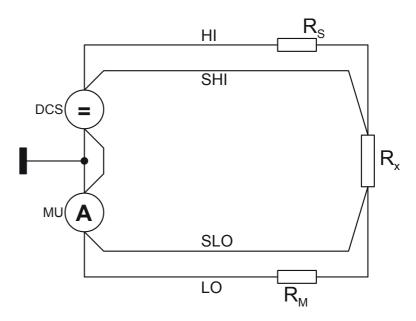

| Figure 10-9  | Guarded 3-wire impedance measurement                                   | 10-13 |

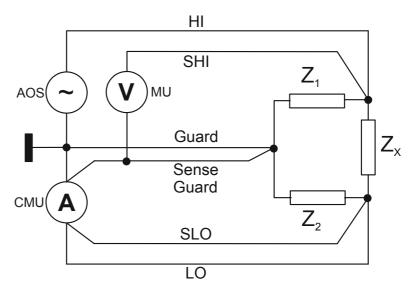

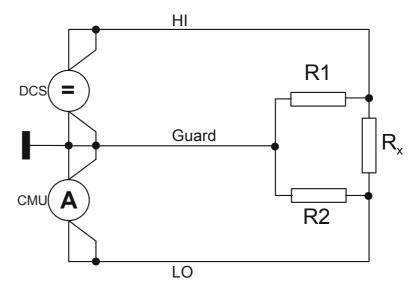

| Figure 10-10 | Guarded 4-wire impedance measurement                                   | 10-14 |

| Figure 10-11 | Guarded 6-wire impedance measurement                                   | 10-14 |

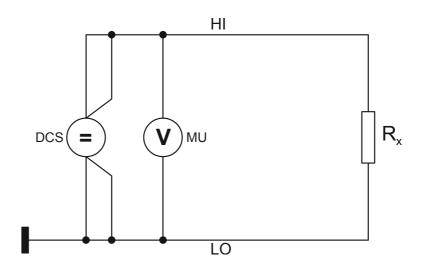

| Figure 10-12 | 2-wire resistor measurement mode C                                     | 10-18 |

| Figure 10-13 | 2-wire resistor measurement mode V                                     | 10-19 |

| Figure 10-14 | 4-wire resistance measurement mode CS                                  | 10-20 |

| Figure 10-15 | 4-wire resistor measurement mode VS                                    | 10-21 |

| Figure 10-16 | Guarded 3-wire resistor measurement                                    | 10-22 |

| Figure 10-17 | Guarded 4-wire resistor measurement                                    | 10-22 |

| Figure 10-18 | Guarded 6-wire resistor measurement                                    | 10-23 |

| Figure 10-19 | Transistor test (voltage measurements)                                 | 10-25 |

| Figure 10-20 | Transistor Beta test                                                   | 10-26 |

| Figure 10-21 | Zener Diode test                                                       | 10-28 |

| Figure 10-22 | Zener Diode test ( > 50 V, cascaded)                                   | 10-28 |

| Figure 10-23 | Zener Diode Test, Adapter Cabling for Voltage > 50 V                   | 10-30 |

| Figure 11-1  | Program sub-window                                                     | 11-1  |

|              |                                                                        |       |

## Enhanced Generic Test Software Library R&S EGTSL

Figures

| Figure 11-2 | Variant identification                                            | 11-4        |

|-------------|-------------------------------------------------------------------|-------------|

| Figure 11-3 | Deactivated variants                                              | 11-5        |

| Figure 12-1 | Debugger                                                          | 12-2        |

| Figure 12-2 | Measurements with transient process                               | 12-9        |

| Figure 12-3 | Measurement with superimposed interference                        | 12-10       |

| Figure 12-4 | Measurements with wide scatter                                    | 12-11       |

| Figure 12-5 | Measurements with narrow scatter                                  | 12-11       |

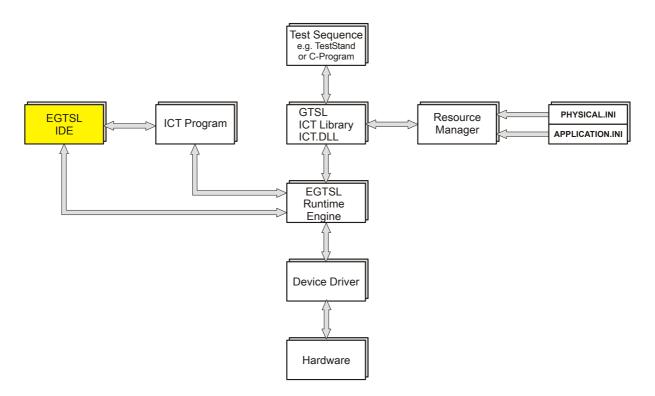

| Figure 13-1 | Opening R&S EGTSL IDE using test library (software structure)     | 13-1        |

| Figure 13-2 | Opening R&S EGTSL IDE using R&S EGTSL Loader (software structure) | 13-5        |

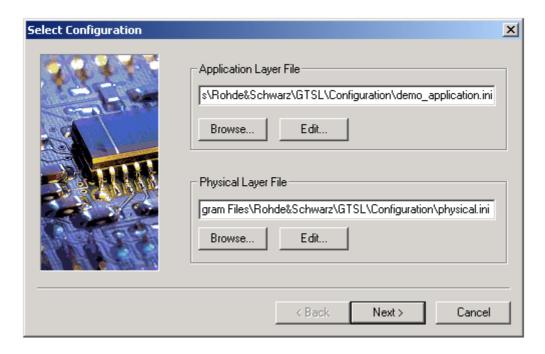

| Figure 13-3 | R&S EGTSL Loader Select Configuration                             | 13-6        |

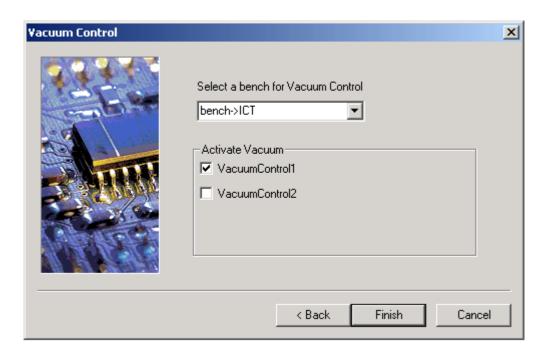

| Figure 13-4 | R&S EGTSL Loader Vacuum Control                                   | 13-8        |

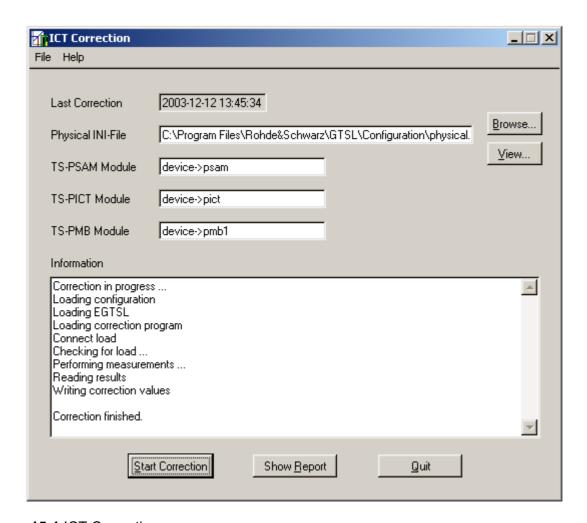

| Figure 15-1 | ICT Correction                                                    | 15-2        |

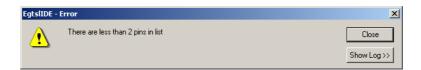

| Figure 16-1 | Runtime Error window (Example 1)                                  | 16-2        |

| Figure 16-2 | Error window, expanded view (Example 1)                           | 16-2        |

| Figure 16-3 | Runtime Error window (Example 2)                                  | 16-2        |

| Figure 17-1 | Test Properties Info                                              | 17-3        |

| Figure 17-2 | Software structure                                                | 17-5        |

| Figure 17-3 | LabWindows CVI, project window                                    | 17-9        |

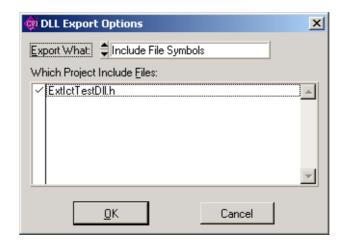

| Figure 17-4 | LabWindows/CVI, DLL Export Options                                | 17-9        |

| Figure 17-5 | Bitmap Layout                                                     | 17-15       |

| Figure 17-6 | Result Tbl sub-window                                             | 17-28       |

| Figure 17-7 | ICT program with 3 blocks                                         | 17-38       |

| Figure 17-8 | Block formation with Prolog/Epilog                                | 17-39       |

| Figure A-1  | Circuit, example 1                                                | <b>A</b> -1 |

| Figure B-1  | Circuit, example 2                                                | B-1         |

Figures

6th Issue 08.06

## **Tables**

| Table 2-1  | File structure                        | 2-8  |

|------------|---------------------------------------|------|

| Table 5-1  | Determination of measured value (1/2) | 5-39 |

| Table 5-2  | Determination of measured value (2/2) | 5-39 |

| Table 7-1  | Character set for names               | 7-2  |

| Table 7-2  | Maximum character lengths             | 7-2  |

| Table 7-3  | Standard keywords of [Device] section | 7-3  |

| Table 7-4  | Standard keywords of [Bench] section  | 7-4  |

| Table 7-5  | Keywords of [ResourceManager] section | 7-5  |

| Table 7-6  | Keywords of [Extlct] section          | 7-5  |

| Table 7-7  | Description of PHYSICAL.INI           | 7-7  |

| Table 7-8  | Description of APPLICATION.INI        | 7-10 |

| Table 8-1  | BDL example RESISTOR                  | 8-16 |

| Table 8-2  | BDL example VAR_RES                   | 8-17 |

| Table 8-3  | BDL example POTI                      | 8-18 |

| Table 8-4  | BDL example RESISTOR_ARRAY            | 8-20 |

| Table 8-5  | BDL example CAPACITOR                 | 8-21 |

| Table 8-6  | BDL example POL_CAP                   | 8-22 |

| Table 8-7  | BDL example INDUCTOR                  | 8-24 |

| Table 8-8  | BDL example DIODE                     | 8-26 |

| Table 8-9  | BDL example Z_DIODE                   | 8-28 |

| Table 8-10 | BDL example TRANSISTOR                | 8-30 |

| Table 8-11 | BDL example                           | 8-31 |

| Table 8-12 | BDL example IC                        | 8-32 |

| Table 8-13 | BDL example CONNECTOR                 | 8-33 |

| Table 8-14 | BDL example BLACK_BOX                 | 8-34 |

| Table 8-15 | BDL example TRACK                     | 8-35 |

| Table 8-16 | BDL example NODE                      |      |

| Table 9-1  | Possible analog tests                 | 9-11 |

Tables

6th Issue 08.06

## 1 General

#### 1.1 User information

This software description applies to the following ROHDE & SCHWARZ products:

R&S TS-LEGT 1143.4140.02 Enhanced R&S GTSL Software for ICT

R&S TS-LEG2 1166.3992.02 Enhanced R&S GTSL Software for Basic ICT on R&S TS-PSAM

#### 1.2 Reference documents

The Enhanced Generic Test Software Library R&S EGTSL is part of the Generic Test Software Library R&S GTSL. For this reason, the following documentation is to be noted in addition to this software description:

Software Description Generic Test Software Library R&S GTSL

The related test hardware is required for performing in-circuit tests. The test hardware is described in the following documentation:

- User Manual Test System Versatile Platform R&S CompactTSVP TS-PCA3

- User Manual Test System Versatile Platform R&S PowerTSVP TS-PWA3

- User Manual Analog Source and Measurement Module R&S TS-PSAM

- User Manual ICT Extension Module R&S TS-PICT

- User Manual Matrix Module B R&S TS-PMB

- Documentation of the test adapter

## 1.3 Explanation of Symbols

Certain text passages in this software description are specially highlighted. The passages marked in this way have the following significance:

#### **CAUTION!**

Failure to follow instructions can result in incorrect measurements.

#### NOTE:

Highlights important details to which special attention must be paid and that make your work easier.

## 2 Software installation

#### 2.1 General

#### NOTE:

Enhanced Generic Test Software Library R&S EGTSL is installed using the installation routine for the Generic Test Software Library R&S GTSL.

To install the <u>Generic Test Software Library R&S GTSL under WINDOWS 2000/XP</u>, the user must be logged in as administrator or as a user with administrator rights.

For additional information on the deinstallation of previous versions of the Generic Test Software Library R&S GTSL or concerning installation, consult the README.TXT file on the installation CD.

Users of the Enhanced Generic Test Software Library R&S EGT-SL are individually responsible for loading operating system updates (patches) and setting up and updating a virus scanner.

#### 2.2 Installation

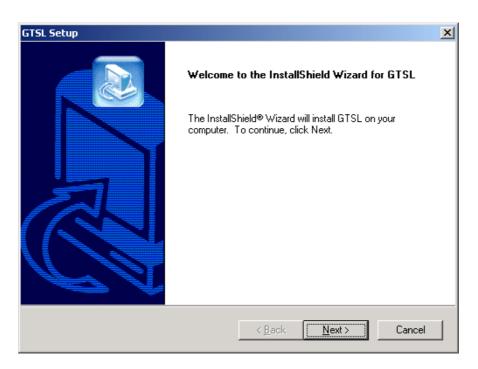

The Generic Test Software Library R&S GTSL is installed on the computer of the Test System Versatile Platform R&S CompactTSVP via an installation routine. Start the installation routine as follows:

- Insert the CD containing the Generic Test Software Library R&S GTSL.

- 2. Start the installation routine by selecting **Start** -> **Run** and typing "X:\Setup.".

- X:\ is the drive letter of the CD-ROM drive.

- 3. Then follow the on-screen installation instructions.

A Welcome screen with installation wizard.

Figure 2-1 Setup Welcome Screen

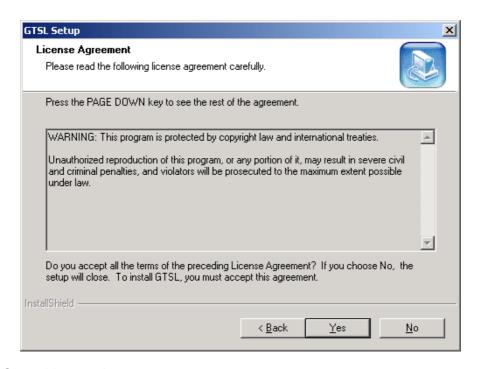

B Accept the License Agreement.

Figure 2-2 Setup License Agreement

6th Issue 08.06

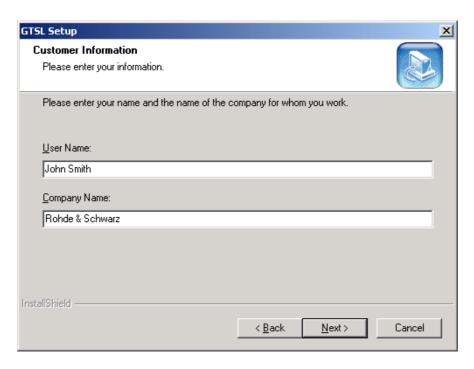

C Enter a user name and company name.

Figure 2-3 Setup User Information

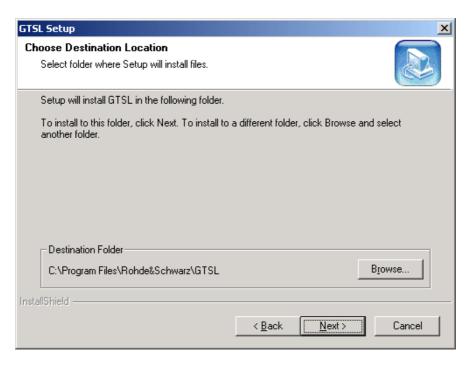

D Select the directory where the R&S GTSL is to be installed.

Figure 2-4 Setup Choose Destination Location

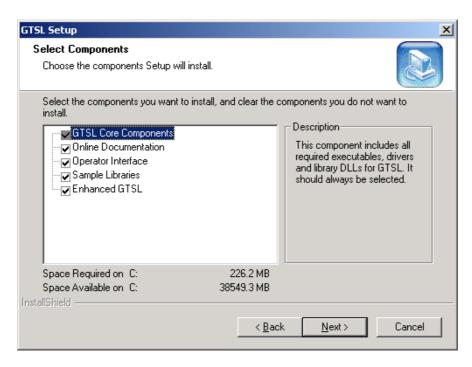

E Select the program components to be install.

Figure 2-5 Setup Select Program Components

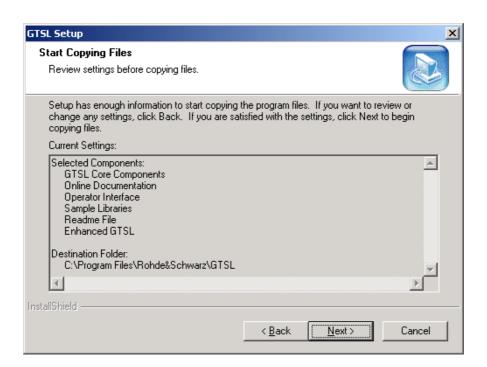

F Display of the current setup settings.

Figure 2-6 Setup Settings

G Display of the Setup Status

Figure 2-7 Setup Status

H Close the installation routine.

Figure 2-8 Setup Complete

#### **Software installation**

## **Enhanced Generic Test Software Library R&S EGTSL**

During the installation process, the following programs are copied to the predefined file structure:

- Test libraries with help files

- Configuration files and calibration files

- Examples for the creation of test libraries

- Documentation

- Examples of test sequences

- Enhanced Generic Test Software Library R&S EGTSL

- Examples and templates of ICT programs

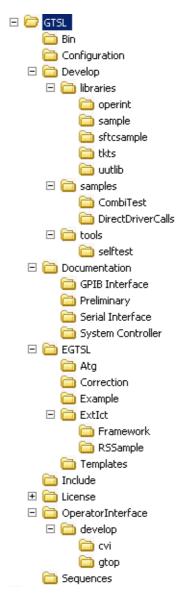

#### 2.3 File structure

The test libraries, test sequences, examples, tools and documentation supplied by ROHDE & SCHWARZ are stored in fixed directories at the time of installation. The files from the corresponding directories are addressed from the TestStand Sequence Editor or other programs. ROHDE & SCHWARZ specify the following structure:

Figure 2-9 File structure

#### NOTE:

The file structure and the directory names below the GTSL directory must be maintained.

| Directory                                               | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GTSL                                                    | Generic Test Software Library. The root directory for the R&S GTSL software can have any name.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bin                                                     | Contains the test libraries (DLL, LIB) and the help files belonging to the test libraries (HLP). The program files for the utilities in R&S GTSL are also in this folder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Configuration                                           | Contains the Physical Layer Configuration File (Physical.INI) and the Application Layer Configuration Files (Application.INI) for various example applications. The files marked with the text "SFT" are needed for the self-test. This folder also contains the calibration data.                                                                                                                                                                                                                                                                                                                                                                   |

| Develop Libraries operint sample sftcsample tkts uutlib | The folder\operint contains an example for the adaptation of the user interface. The directory\sample contains a generally valid example for the creation of a test library. The folder\sftsample contains an example for the preparation of a custom self-test or the customer-specific adaptation of the self-test provided. The folder\tkts contains an example for the adaptation of the Toolkit for Teststand. The directory\uutlib contains an extended example for the creation of a test library for customer-specific communication with the mobile phone being tested. The directories contain the C source code of the example libraries. |

| Develop samples CombiTest DirectDriverCalls             | The folder \CombiTest contains an example for a combinational test (in-circuit and functional test).  The folder \DirectDriverCalls contains an example how to mix R&S GTSL library and device driver calls.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Develop<br>tools<br>selftest                            | This folder contains the TSVP self-test including the executable and the C source code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Documentation                                           | Contains the various items of documentation in the form of PDF files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EGTSL<br>Atg                                            | Contains the files for the execution of the Automatic Test Generator ATG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EGTSL<br>Correction                                     | Contains the utility ICTCorrection with the correction data determined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

**Table 2-1** File structure

| Directory                       | Contents                                                                                                                                                                                                                                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EGTSL<br>Examples               | Contains the examples described in the software description R&S EGTSL.                                                                                                                                                                      |

| EGTSL Extlct Framework RSSample | The folder\Framework contains the framework code for the creation of a user-defined ICT extension library.  The folder\RSSample contains an example for the creation of a user-defined ICT extension library with source-code and binaries. |

| EGTSL templates                 | Contains a template for the preparation of a new ICT program on the R&S EGTSL user interface.                                                                                                                                               |

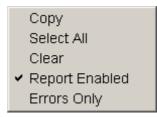

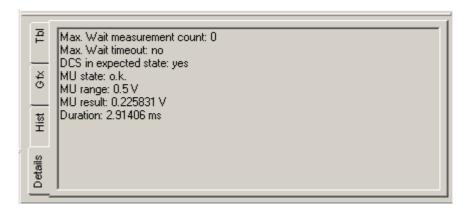

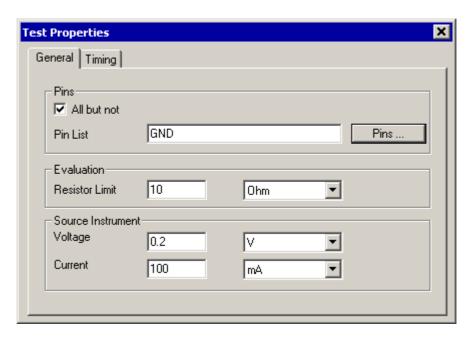

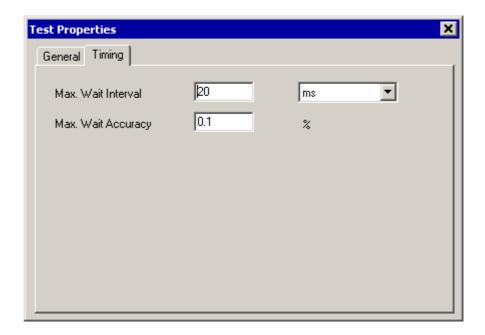

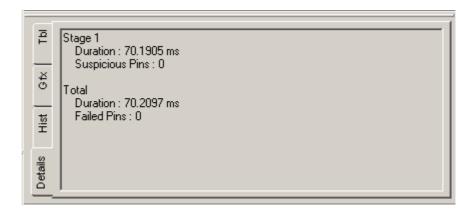

| Include                         | Contains the h-files (include files) needed for the development of new test libraries.                                                                                                                                                      |